# INVESTIGATION INTO HIGH EFFICIENCY DC-DC CONVERTER TOPOLOGIES FOR A DC MICROGRID SYSTEM

Thesis submitted for the degree of Doctor of Philosophy at the University of Leicester

by

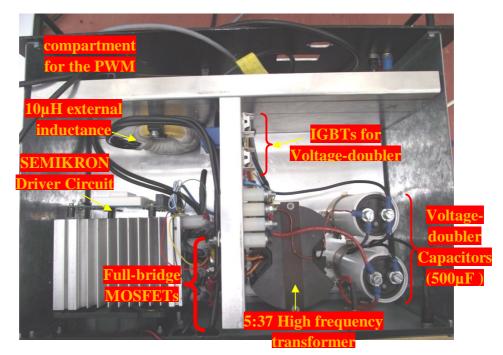

Oday Ahmed

Electrical Power and Power Electronics Group Department of Engineering University of Leicester Leicester, United Kingdom

December 2011

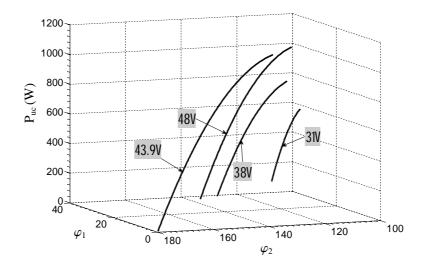

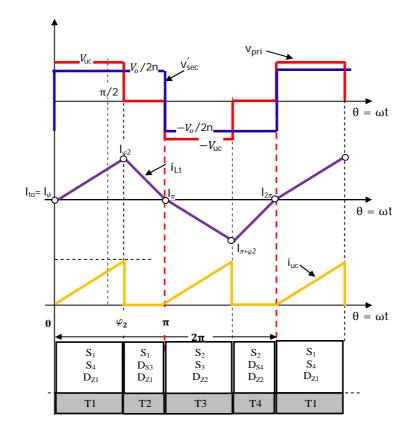

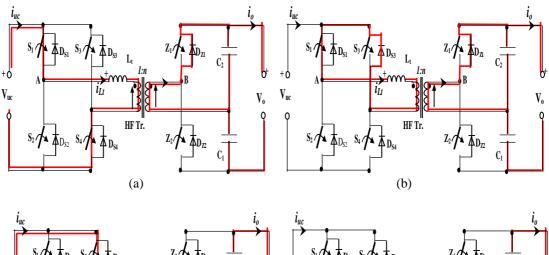

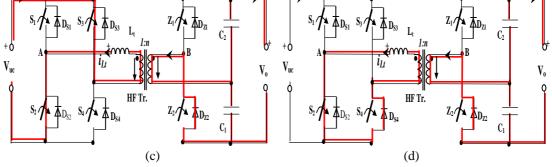

# Investigation into High Efficiency DC-DC Converter Topologies for a DC Microgrid System

Oday Ahmed

# Abstract

Distributed generation in the form of DC microgrids has recently attracted increasing research interest. For integrating primary sources and energy storage devices to the DC bus of a DC microgrid power electronic converters are necessary, but the associated losses may degrade the microgrid efficiency. Therefore, the aim of this work is to develop high-efficiency converters, particularly for fuel cell generators and ultracapacitors energy buffers suitable for use in a stationary distribution system. Based on the evaluation of the fuel cell dynamic performance, a current-fed DC-DC converter design with a lower voltage rating of the switching devices and a higher DC voltage conversion ratio is proposed. A number of optimisation approaches have been applied to further improve the converter efficiency over its full power range. The periodic steady state operation of the converter is analysed in detail; state-space averaging is then used to determine the small signal equations and derive transfer functions. A closed controller has designed and verified loop been by а novel PSpice/Simulink/actual processor co-simulation approach, where the modelling results are validated by experimental results using a modelbased design method.

To sustain the charging and discharging states of the ultracapacitor, a bidirectional DC–DC converter is required. Based on a comprehensive overview on different DC–DC converter topologies, the research presented here has shown that, bidirectional voltage–fed topology is better suited for dealing with the fast dynamic response of the ultracapacitor. But for a wide input voltage variation, this topology exhibits a higher circulating power flow and higher conduction losses as a consequence. Therefore, a detailed analysis of the bidirectional converter exploring the impact of the circulating power flow interval is developed in this study. Analytic methods have been applied to establish the optimal operation of the bidirectional voltage–fed converter for an ultracapacitor to improve its performance and efficiency. Based on these methods, a novel modulation scheme is proposed that minimises the circulating power flow in the converter, that has been verified by detailed simulation.

I dedicate this thesis to my parents, wife and sons

# Acknowledgements

First, I would like to thank Dr. Hans Bleijs, my supervisor here at University of Leicester. His guidance, support, patience and personal time throughout my years as a PhD student have been truly appreciated. Also his comments and suggestions during the writing of this thesis are invaluable and are highly appreciated.

Special thanks are given to my colleague Mr Luigi Alessandro, for his technical help in the construction of the prototype converter and shared a lot of ideas for this work.

Also I would like to thank the Iraqi Ministry of Education for granting a PhD scholarship.

I am grateful and thank all of those who assisted me in my PhD study at Department of Engineering.

Most importantly, I would like to thank my family (mother, father, wife, and brothers) and friends for their support throughout all the years.

# List of Contents

| Chapter One: Introduction                                                     |     |

|-------------------------------------------------------------------------------|-----|

| 1.1 State of The Art Microgrid Systems                                        | 1   |

| 1.2 Microgrid Configurations                                                  |     |

| 1.2.1 AC Microgrid Configuration                                              |     |

| 1.2.2 DC Microgrid Configuration                                              | 4   |

| 1.3 Microgrid Energy Sources                                                  | 6   |

| 1.3.1 Photovoltaic                                                            | 7   |

| 1.3.2 Wind Energy Conversion System                                           | 7   |

| 1.3.3 Cogeneration System                                                     | 8   |

| 1.3.4 Energy Storage                                                          | 9   |

| 1.3.5 Fuel Cell Generator                                                     | 9   |

| 1.4 Power Electronic Interface Circuit for a Microgrid                        | 11  |

| 1.5 Objectives of the Thesis                                                  | 12  |

| 1.6 Outline of the Thesis                                                     | 12  |

| Chapter Two: Fuel Cell–Ultracapacitor DC Microgrid System                     | 14  |

| 2.1 Introduction                                                              | 14  |

| 2.2 FC Power Generator                                                        | 15  |

| 2.2.1 Principle of Operation                                                  | 15  |

| 2.2.2 Voltage-Current Characteristics of FC                                   | 16  |

| 2.2.3 Constraints on FC Current                                               | 19  |

| 2.2.4 Dynamic Performance of the Ballard FC System                            | 19  |

| 2.3 Ultracapacitor Energy Buffer                                              | 26  |

| 2.3.1 Principle of Operation                                                  |     |

| 2.3.2 Electrical Characteristic of Ultracapacitor                             |     |

| 2.3.3 Dynamic Modelling of the Maxwell Ultracapacitor                         | 29  |

| 2.4 Configurations of Fuel Cell–Ultracapacitor DC Microgrid                   |     |

| 2.4.1 Overview of Configurations                                              | 34  |

| 2.4.2 Power Flow Management and Control Strategy                              |     |

| 2.5 Topologies of Fuel Cell and Ultracapacitor Power Converters               |     |

| 2.5.1 Unidirectional DC-DC Converters                                         | 43  |

| 2.5.2 Isolated Bidirectional DC-DC Converters                                 | 56  |

| 2.6 Conclusions                                                               |     |

| Chapter Three: Fuel Cell CFC with High Voltage Step-Up and Low Switch Voltage | e   |

| Ratings                                                                       |     |

| 3.1 Introduction                                                              |     |

| 3.2 Steady-State Analysis of the Proposed CFC                                 |     |

| 3.2.1 Operational Principle                                                   |     |

| 3.2.2 DC/DC Voltage Conversion ratio                                          |     |

| 3.2.3 Soft-Switching Range                                                    |     |

| 3.2.4 Input Current Ripple                                                    |     |

| 3.3 Further Efficiency Improvements and Design Considerations                 |     |

| 3.3.1 Analysis and Remedies of Effects of the Parasitic Elements              |     |

| 3.3.2 Optimisation of Active-Clamp Circuit                                    |     |

| 3.3.3 Selection of the Dead time                                              |     |

| 3.4 Comparative Results                                                       |     |

| 3.4.1 Evaluation of the Proposed FBCFC Features                               | 117 |

| 3.4.2 Efficiency Comparison                                                      | .120 |

|----------------------------------------------------------------------------------|------|

| 3.5 Conclusions.                                                                 | .123 |

| Chapter Four: Dynamic Modelling and Digital Control of a Fuel Cell Converter Sys | tem  |

|                                                                                  |      |

| 4.1 Introduction                                                                 |      |

| 4.2 Development of the Mathematical Dynamic Model                                | .127 |

| 4.2.1 Derivation of State–Space Equations                                        |      |

| 4.2.2 Derivation of State-Space Averaging Model                                  |      |

| 4.2.3 Small-Signal Model and AC Equivalent Circuit Derivation                    |      |

| 4.3 Controller Design and Analysis                                               |      |

| 4.3.1 Direct Duty Cycle Control                                                  |      |

| 4.3.2 Current–Mode Control                                                       |      |

| 4.4 Comparison of Dynamic Performance of the Proposed CFC with Other FB          |      |

| Topologies                                                                       |      |

| 4.4.1 FBCFC with Voltage–Doubler Rectifier Diode without Active–Clamp Cir        |      |

| (Config.2)                                                                       |      |

| 4.4.2 FBCFC with Active-Clamp Circuit (Config.3)                                 |      |

| 4.5 Verification of Dynamic Model and Control System                             |      |

| 4.5.1 Small-Signal Mathematical Model Approach                                   |      |

| 4.5.2 Physical Components Model Approach                                         |      |

| 4.6 Implementation and Validation of the Controller System                       |      |

| 4.6.1 MBD Approach Features                                                      |      |

| 4.6.2 Selection of Embedded DSP                                                  |      |

| 4.6.3 Control Algorithm Validation                                               |      |

| 4.6.4 Control Algorithm: Testing and Performance                                 |      |

| 4.7 Conclusion                                                                   |      |

| Chapter Five: Controlling Power Flow Methods for the Bidirectional Converter: A  | .109 |

| Comparative Study                                                                | 170  |

| 5.1 Introduction                                                                 |      |

| 5.2 Conventional Phase-Shift Modulation Scheme                                   |      |

| 5.2.1 SSW Analysis                                                               |      |

| 5.2.1 SSW Analysis                                                               |      |

| 5.2.2 KWS Analysis                                                               |      |

|                                                                                  |      |

| 5.3.1 Triangular Current Modulation                                              |      |

| 5.3.2 Modified Triangular Current Modulation                                     |      |

| 5.3.3 Hybrid Modulation Schemes                                                  | .190 |

| 5.3.4 Voltage-Balance Modulation Scheme                                          |      |

| 5.4 Comparison of Modulation Schemes and Conclusions                             |      |

| Chapter Six: New Modulation Scheme for an UC Bidirectional DC-DC Converter       |      |

| 6.1 Introduction.                                                                |      |

| 6.2 Switching Control Strategy and Design Considerations                         |      |

| 6.2.1 Switching Control Strategy                                                 |      |

| 6.2.2 Design Considerations                                                      |      |

| 6.3 Circulating Power Flow (CPF) Analysis                                        |      |

| 6.3.1 Definition of CPF Interval                                                 |      |

| 6.3.2 Determination of CPF Interval                                              |      |

| 6.3.3 Impact of the CPF Interval on the Converter Parameters                     |      |

| 6.4 Operation Principle of the Optimal Modulation Scheme                         |      |

| 6.4.1 Zero CPF Interval Mode                                                     |      |

| 6.4.2 Inner Single Phase-Shift Mode                                              | .233 |

| 6.4.3 Minimum CPF Interval Mode                                                            | 236   |

|--------------------------------------------------------------------------------------------|-------|

| 6.4.4 Combination of the Modulation Schemes                                                | 238   |

| 6.5 Evaluation of the Proposed Modulation                                                  | 243   |

| 6.6 Conclusions                                                                            |       |

| Chapter Seven: Conclusions, Original Contributions and Suggestions for Future V            | Vork  |

|                                                                                            | 262   |

| 7.1 General Conclusions                                                                    | 262   |

| 7.2 Original Contributions                                                                 | 263   |

| 7.3 Suggestions for Future Work                                                            | 267   |

| Appendix A: FC Source Model Using Parameters Extracted from Measurements                   | 269   |

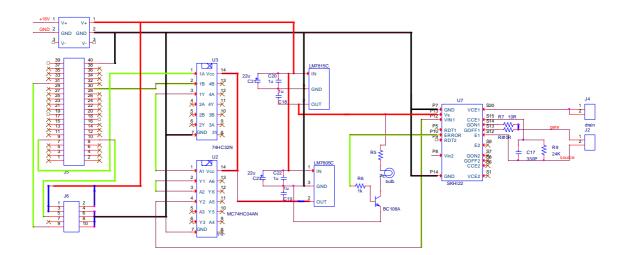

| Appendix B: DSP–PWM Interface Circuit                                                      |       |

| Appendix C: Averaging the Boost Inductor Current Waveform                                  | 274   |

| Appendix D: Full Derivation of the Control-to-Output Transfer Function G <sub>vd</sub> (s) | 275   |

| Appendix E: Elimination of the Fraction Period Duty Cycle $\delta(t)$ from State-Space     | ce    |

| Equation (4.21)                                                                            |       |

| Appendix F: Matlab Code for the Transfer Function Gvd(s) of Config.2, Config.3             | and   |

| Proposed Configuration.                                                                    |       |

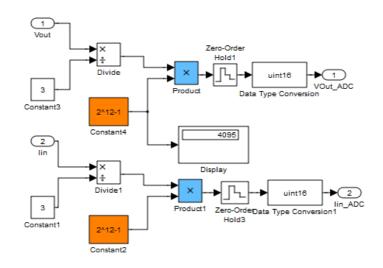

| Appendix G: PSpice and Simulink Circuit Diagrams for the CFC                               | 280   |

| Appendix H: Overlap PWM Generation for the FBCFC                                           | 282   |

| Appendix I: Example Shows How the "Mathematica" Software Tool are Used to                  | Drive |

| the Equations in Chapter 5 and 6                                                           |       |

| Appendix J: Average Power and Phase-Shift Angles Values that have been Used                | for   |

| Different Operating Modes                                                                  | 287   |

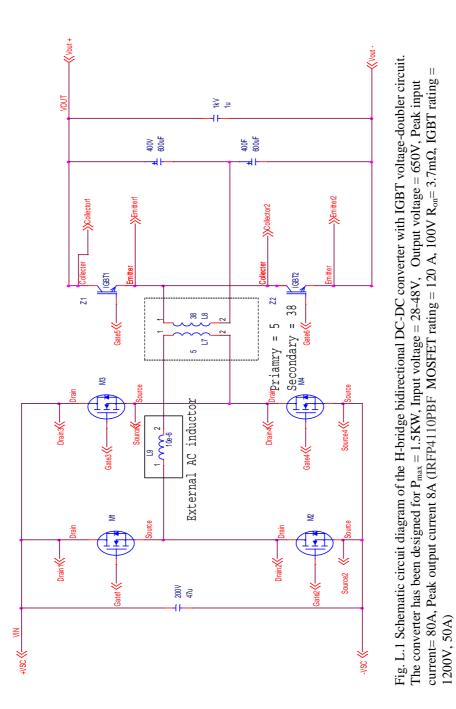

| Appendix K: PSpice and Simulink Circuit Diagrams for the BDC                               | 288   |

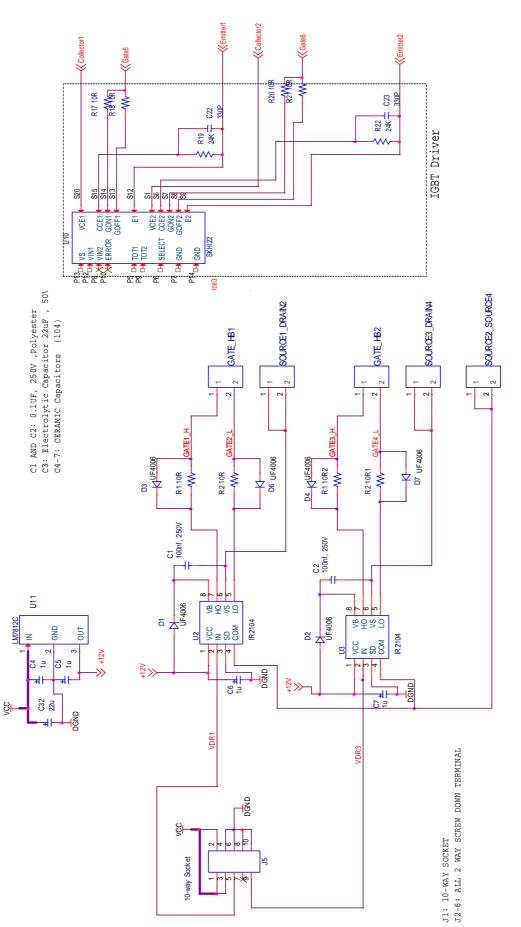

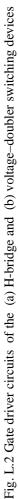

| Appendix L: Schematic Diagrams of the BDC, Switch Driver Circuits, and DSP-                | PWM   |

| Interfacing Circuit                                                                        | 295   |

| Appendix M: Control Algorithm of the Proposed Optimal Modulation Scheme                    | 298   |

| Glossary and Terms                                                                         | 301   |

| List of Symbols                                                                            | 301   |

| Abbreviations                                                                              |       |

| References                                                                                 | 305   |

| List of Author's Publications                                                              | 315   |

**Chapter One**

# Introduction

#### 1.1 State of The Art Microgrid Systems

Traditional power systems are facing a number of problems such as low energy efficiency, environmental pollution, drastic increases of the fossil fuel prices and gradual depletion of fossil fuel resources. These problems have led to the development of a new concept for power generation so as to generate electricity locally by utilising small non-conventional and renewable energy sources such as microturbines, back-up diesel generators, wind turbines, solar photovoltaic cells, and fuel cells [1]. This kind of power generation called a "distributed generation" system. In distributed generation systems the electricity is generated very close to the consumption sites. This leads to a reduction of the energy lost on long transmission lines and reduces the size and number of the power lines. The increase in distributed generation penetration depth and the presence of multiple distributed generation units in electrical network within a certain local area in close proximity to one another have brought about the concept of the "microgrid" [2].

A microgrid is defined as a localised grouping of electrical and thermal loads with power generators and energy storage. It includes one or more distributed generation units capable to operate with the centralised grid but it can also be operated isolated from the grid while supplying continuous power to various load [3]. The microgrid is responsible for dealing with the requirements of its consumers, providing high power quality and possibly controlling some of the non-critical loads [4]. The key distinction of the microgrid from a conventional power generation is that the power generators are small, they are distributed and located in close proximity to the energy users. Microgrids have various benefits such as improvement of the power quality and reliability of electricity and an increase in the penetration of renewable energy resources to the distribution networks. Due to the close proximity to consumption sites, microgrids are anticipated to provide additional benefits to customers and service providers [5, 6]

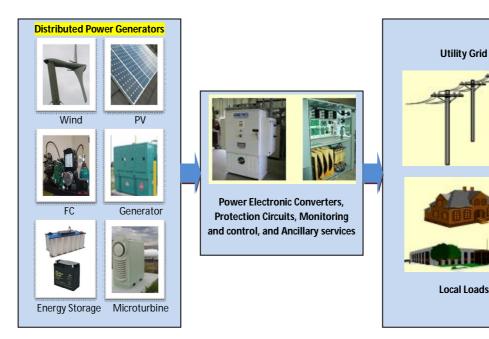

Fig. 1.1 shows the conceptual parts of microgrid where various power generators are connected to corresponding loads and a utility grid via power electronic converters.

Fig. 1.1 A typical microgrid parts

In the following the configurations of microgrids are introduced together with some of the power generators widely used in microgrids. In addition the major role of the power electronics in the microgrid is shown.

#### **1.2 Microgrid Configurations**

Microgrid architectures for integrating renewable energy resources can be classified into AC or DC bus interconnections. A DC microgrid is a system whose different alternative energy sources are connected to a main DC bus-bar through appropriate power electronic interfacing circuits and then the DC bus-bar is connected DC loads. It can also be connected to an AC grid or AC user loads through a DC–AC converter (inverter) which can be bi-directional. An AC microgrid is a system whose different energy sources and loads are interconnected to an AC grid, where necessary through appropriate power electronic circuits.

### **1.2.1 AC Microgrid Configuration**

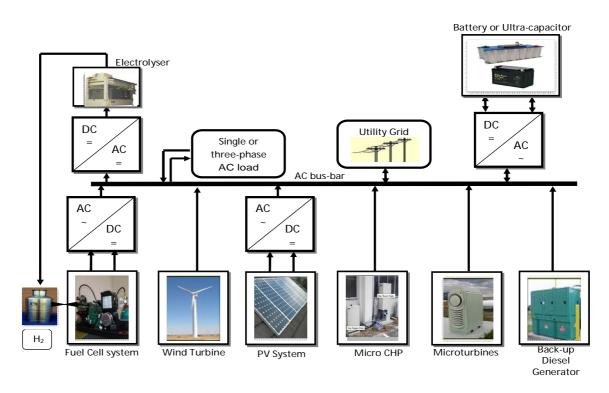

In the AC microgrid, shown in Fig. 1.2, all the DC and AC sources are connected to the AC utility grid via AC bus-bar. DC sources such as photovoltaic generators and fuel cells are connected to the AC bus through DC–AC inverters and sometimes they also require a DC–DC boost converter as a front-end to step up their low input voltage. In an AC microgrid synchronisation of all AC generators and output of the power converters of the DC sources and energy stores is necessary. Furthermore, due to the non–linear characteristics of power electronics converters, power factor correction and topologies with sophisticated control strategy for harmonic distortion reduction are needed to improve the power quality of the AC bus. Moreover, rapid variations in the output of the renewable sources can lead to excessive voltage and frequency variations of AC bus of an AC microgrid. This can limit the maximum penetration of renewable energy sources into an AC microgrid bus.

Fig. 1.2 Block diagram of an AC microgrid system

Recently, DC microgrids have show promising features such as improving the grid efficiency and the power quality in addition to increase the penetration of the renewable energy sources to the microgrid bus and elimination of DC–AC power conversion stage required in AC microgrid for the renewable sources and loads. Thus, some negative effect associated with AC microgrid can be avoided.

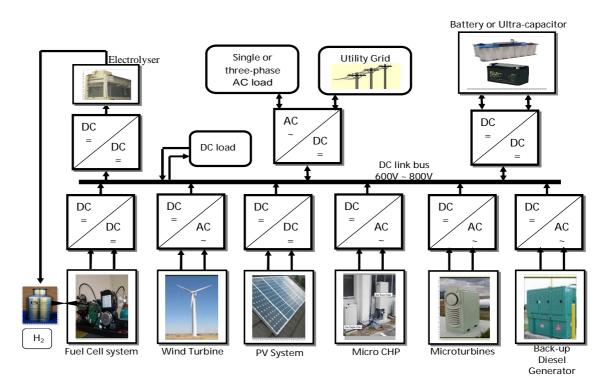

#### **1.2.2 DC Microgrid Configuration**

Fig. 1.3 shows the basic configuration of DC microgrid. As can be seen the DC microgrid may comprise both dispatchable power generators such as a fuel cell, back-up diesel generator or micro (gas) turbines, and non-dispatchable generators, such as solar photovoltaic and wind turbines, and energy storage, in the form of ultracapacitors or batteries. In the DC microgrid configuration, all of the above generators and storage units are connected to the DC bus-bar.

Fig. 1.3 Basic configuration of the DC microgrid system

The AC generators such as the wind turbine, microturbine and back-up diesel generators are connected to the DC bus through an AC–DC converter. For grid-connected operation the power transfers from different generators and storages to the utility grid and AC loads through the main bidirectional DC–AC inverter as shown in Fig. 1.3. The back-up diesel generator and the fuel cell should provide the peak load and charge the short-term storage units simultaneously, while the utility grid through the inverter can maintain the voltage level of the DC bus and cover the required load demand if the DC microgrid fails.

Referring to Fig. 1.3, it can be seen that different configurations of power electronic converters are used to interface these generation resources to a common DC bus-bar. These converters are employed to manage the power flow between the generators, the storage sources and the load and to regulate the DC bus voltage regardless of the voltage variations of their inputs.

The DC microgrid system has the following advantages over the AC microgrid [7-9]:

- Synchronisation of power generators is not needed.

- Unlike AC microgrids, loads connected to the DC bus are not affected by voltage sag and three-phase voltage unbalance and voltage harmonics.

- The power generators and energy storage sources with the DC microgrid are operated cooperatively to control the DC bus voltage and to improve the power quality of the grid.

- Energy storage devices are used in the DC microgrid to compensate power fluctuations caused by the energy sources such as the wind turbine.

- The DC microgrid can supply power to the loads connected with the DC bus when the AC utility line experience abnormal or fault conditions.

- Aside from reducing CO<sub>2</sub> emissions and financial costs, DC microgrids may provide the best solution for increasing the penetration of renewable energy sources in a distribution network, improving the system efficiency and also making plug-and-play grids conceivable.

The disadvantage of this configuration is that the whole microgrid system fails to supply AC power if the DC–AC inverter is out of service. In addition, the multiple power converters required in a DC microgrid may add additional loss to the system operation. Therefore, further research is required to improve the performance and the system efficiency of the converters.

#### **1.3 Microgrid Energy Sources**

The key feature of the microgrid is that there should be local electricity generation that matches the load requirements in the microgrid. There are various types of distributed generation resources that may be considered such as photovoltaic cells, fuel cells, wind turbines, micro combined heat and power (micro-CHP), etc. An overview of some of the clean generation systems is given below.

#### **1.3.1** Photovoltaic

Photovoltaic (PV) cells can convert sunlight directly into electricity using the photovoltaic effect [10]. The cost of PV has declined considerably since the first solar cell was manufactured. A photovoltaic generator consists of a number of modules, formed by the interconnection of photovoltaic cells, connected together in series and parallel to provide the required voltage and current. The output power of PV systems ranges from a few watts for portable applications such as calculators, to megawatt power stations [11]. Photovoltaic arrays integrated in the roofs and facades of buildings are becoming an increasingly common method of power generation within the urban environment. PV is a DC generator source, therefore a DC–AC inverter is required to convert the DC power into AC power at the specified frequency and voltage level and then interfaced with the AC utility grid and loads. For stand-alone or grid connection, PV system can be combined with energy buffer to store the energy in order to be used when the sun is not shining. While PV cells can be effectively used as a source in a microgrids, it they suffers currently from high installation costs and low energy efficiency [9].

# 1.3.2 Wind Energy Conversion System

A wind energy conversion system (WECS) converts wind energy into electrical energy [1]. Wind as a type of renewable energy has received considerable attention for producing electricity in comparison with other distributed generation resources due to its cost, rapid technological development and the power rating produced by the WECS.

The main component of a WECS is the turbine. This is coupled to the generator either directly (if a multi–pole generator is used) or through a step–up gearbox. The main parts of a wind turbine are the tower, the rotor and the nacelle [1, 9].

Due to the stochastic nature of the wind generators suffer from rapid variations, potentially leading to deviations in the output voltage and frequency, and this limits the penetration of these generators in microgrid [12]. To overcome this problem the wind turbine generators can be incorporated with other power resources such as, back-up diesel generator, energy storage or fuel cells. The energy storage devices such as a battery or ultracapacitor can be used as power assistance for short-term to reduce the intermittency problem of wind generator [13]. But to provide enough energy over time (i.e. for long-term) the integration of PV or fuel cells with wind generator systems appear to be the more efficient and effective solution to the problem of intermittency.

## 1.3.3 Cogeneration System

Cogeneration or combined heat and power systems (CHP) represent one of the most effective approaches to ensure maximum energy efficiency in microgrid applications since it is produces two kinds of energy, electric power and thermal energy. CHP systems capture the waste heat during the production of electricity and convert it into thermal energy. For small scale private use, such as homes or small commercial buildings, micro-CHP systems can be employed [14]. Most large industrial CHP units generate electricity as the primary product with heat as a secondary output while micro-CHP systems generate heat as the primary product with electricity as a by-product [1, 4]. Thus, energy generation of micro-CHP systems is principally dependent on the heat demand of the consumers. Most micro-CHP systems use natural gas for fuel because it is the cleanest fossil fuel, is widely available, and easily transported through pipelines. The CHP system can be connected to the DC microgrid through an AC–DC converter (rectifier) as illustrated in Fig. 1.3.

## **1.3.4 Energy Storage**

In practice an energy storage unit is usually considered an essential requirement for a microgrid to allow instantaneous power balancing of distributed generation resources and loads when the microgrid is disconnected from the utility grid (islanding or autonomous) and to ensure uninterrupted supply to priority loads. In addition, the energy storage devices operate in the microgrid system to store surplus energy. The backup energy storage devices that could be included in microgrids are: storage batteries, flywheels, and ultracapacitors. Most of the storage devices such as batteries and ultracapacitors produce a DC voltage, thus a bidirectional DC–AC converter is required for use in an AC microgrid (see Fig. 1.2) while a bidirectional DC–DC converter is utilised to interface them to the DC bus of a DC microgrid (see Fig. 1.3). In contrast, flywheel generators can directly produce AC and hence may feed directly into the AC bus of the AC microgrid [1, 4]. However, a bidirectional AC–DC converter is necessary to interface the flywheel generator to a DC microgrid bus<sup>1</sup>.

Some storage devices like ultracapacitors store power at high density but are limited in the amount of energy stored, whereas others like flywheels suffer from low power density but are capable of discharge for a longer time [1].

# 1.3.5 Fuel Cell Generator

For the future generation of clean electricity, fuel cell (FC) ranks as one of the dominant technologies. Fuel cells are electrochemical devices that convert the chemical energy of

<sup>&</sup>lt;sup>1</sup> Most of flywheel storage systems use AC–DC–AC conversion stages when connect to AC bus of an AC microgird.

a fuel directly into electrical energy with high efficiency. There are several types of fuel cell, categorised by the type of electrolyte such as proton exchange membrane fuel cell (PEMFC), alkaline fuel cell (AFC), and solid oxide fuel cells (SOFC). Fuel cells have many advantages [9, 13, 15]:

- Fuel cells have the advantage of high power density, and can support the power system for an unlimited time<sup>2</sup>.

- They can be used for stationary as well as automotive power generation.

- Fuel cells generated a DC voltage and the only by-products are water and heat.

- Since it is working with zero emissions the fuel cell can be used for indoor operation.

- Moreover, compared to the PV and wind energy the fuel cells can continuously producing power if the fuel is available.

Despite these advantages, the cost of fuel cell is relatively high<sup>3</sup> in comparison with conventional power generators. In addition fuel cells have a limited lifetime and require a special treatment for the fuel production<sup>4</sup>.

However, the major problem of the fuel cell is that it has a relatively slow dynamic response to sudden load changes because of the slow internal electrochemical reactions and the processing time required for the ancillary equipments such as valve, pumps, and a hydrogen reformer. Therefore, in order to supply electric power to transient loads the fuel cell requires an energy storage system, such as batteries or ultracapacitors, to fill the gap between the output power delivered by the fuel cell and the power required by

<sup>&</sup>lt;sup>2</sup>In a microgrid system storage devices can provide only for short-term power requirements, while fuel cells and back-up diesel generator can supply the long-term power demand.

<sup>&</sup>lt;sup>3</sup>This is due to the very high costs of the catalysts, membrane materials, and fabrication processes for collector plate.

<sup>&</sup>lt;sup>4</sup> Pure hydrogen gas as the main fuel is necessary for some types of fuel cell such as PEMFC.

the load. In addition, energy storage can help to improve the fuel cell performance (see next Chapter for further details).

#### **1.4 Power Electronic Interface Circuit for a Microgrid**

One of most important features of a microgrid is the advanced structure which can facilitate the connections of various AC and DC renewable energy resources, energy storage devices, utility grid and different AC and DC loads with optimal operation and high efficiency. To achieve those goals, power electronics converters plays a very important role in order to interface different sources and loads to a microgrid. Power electronic converters are utilised in microgrids to manage the flow of power and convert it into suitable DC or AC form as required. A number of converter configurations, such as AC–DC rectifiers, DC–DC converters, and DC–AC inverters, are necessary to achieve the many functions within a microgrid, as shown in Fig. 1.2 and Fig. 1.3.

However, power electronic circuits are quite costly due to their complicated technology, they may increase the losses through the microgrid system, and they are the most common sources of harmonics and low power quality for a microgrid bus and resources. Reference [16] describes a new passive AC–DC diode rectifier circuit with step–up voltage properties, developed by the author, that can be employed as a front-end converter for connecting an AC generator to a DC microgrid. It can also be used to maintain the power quality on the AC bus of an AC microgrid system.

Furthermore, reliability and functionality for the selectable power electronics topology is needed [17]. Reliability will allow long term commercial penetration of renewable energy sources using power electronics whilst functionality will expand the exploitation of microgrid and improve power quality.

#### **1.5 Objectives of the Thesis**

The aim of this study is to investigate and develop high-efficiency power electronic converters for the interconnection of elements of a DC microgrid. The main focus is on the power electronic converter topologies for connecting fuel cells and ultracapacitors to a DC microgrid for stationary power distribution systems. The objectives of this research can be divided into the following parts:

- To investigate existing unidirectional and bidirectional DC–DC converter topologies that are suited for the fuel cell and the ultracapacitor energy buffer.

- To develop a new converter topology, optimised for operation with a fuel cell.

- To study the dynamic performance of the fuel cell and the associated power electronics converter to select an appropriate controller design for the developed fuel cell converter.

- To digitally implement and test the proposed fuel cell converter system.

- To develop a dynamic model describing the behaviour of the ultracapacitor that can then be interfaced with a model of the power electronics converter.

- To improve the performance of the ultracapacitor converter by means of a novel modulation scheme to achieve optimum performance.

#### **1.6 Outline of the Thesis**

The structure of the thesis is organised as follows:

In Chapter 2, the characteristics of the fuel cell and the ultracapacitor are described and studied. Experiments have been conducted on a fuel cell to establish the steady-state and the dynamic performance of this source. A model of an ultracapacitor is established

in Matlab. A number of fuel cell–ultracapacitor DC microgrid configurations are presented. The advantages, disadvantages, and features of several unidirectional and bidirectional DC–DC converter topologies for the fuel cell and ultracapacitor applications are discussed. Based on the electrical output characteristics of the fuel cell and the ultracapacitor, appropriate power electronic converter topologies are selected to interface the fuel cell and the ultracapacitor to the DC bus of a DC microgrid.

Chapter 3 presents a detailed steady-state analysis of a new fuel cell converter. Means to improve the converter efficiency are described. A comparison of the proposed converter with other competing fuel cell converter topologies is presented. Experimental results are reported and compared with the results of detailed simulation.

In Chapter 4, a full dynamic model for the fuel cell converter based on the state–space averaging method is derived. The converter dynamic performance is evaluated and compared with that of other configurations using the developed dynamic model. Based on the validated dynamic model a two–loop digital control system for the fuel cell power converter has been designed. Three different approaches have been used to demonstrate the fidelity and effectiveness of the dynamic modelling. The developed controller system has been executed and validated using real processor hardware.

Chapter 5 provides a comparative study of various modulation schemes that can be used to control the power flow of the ultracapacitor bidirectional DC–DC converter.

Chapter 6 details a new optimal modulation scheme to control the power flow of the bidirectional converter is presented, based on a comprehensive mathematical analysis. Theoretical analyses are verified using the detailed simulation results.

Finally, Chapter 7 presents the conclusions on this study and suggestions for future work.

# **Chapter Two**

# Fuel Cell–Ultracapacitor DC Microgrid System

### 2.1 Introduction

As shown in the previous Chapter, a DC microgrid is composed of different dispatchable and non-dispatchable power generators and energy buffers, such as FCs and ultracapacitors, which are employed to provide the steady-state and transient power demanded by the load. To interface these generation resources to a common DC busbar, different configurations of power electronic converters have been proposed in the literature. For the FC, a unidirectional DC–DC converter is utilised, for the ultracapacitor, however, a bidirectional DC–DC converter is needed to maintain the state-of-the-charge (SOC) of the ultracapacitor. The overall efficiency of the microgrid will depend on the efficiency of these converters. High efficiency and low cost converters are very important to obtain a cost-effective solution. In addition, the power electronics converters must be chosen in respect to the characteristics of these generation resources.

This Chapter introduces an overview on different of DC–DC converter topologies and investigates their applicability for FC and ultracapacitor electricity generators based on the electrical output characteristics of these resources. The FC and ultracapacitor characteristics and properties are also introduced in this Chapter. A number of configurations that can be employed to interface the ultracapacitor with the FC generator forming part of a DC bus microgrid are presented.

#### 2.2 FC Power Generator

Fuel cells are static electrochemical devices, which convert the chemical energy of fuel into electrical energy [15]. One of the most popular types of FC for low temperature operation (below or around 200°C) that uses hydrogen as a fuel is the proton exchange membrane fuel cell (PEMFC). The PEMFC can be used for stationary as well as automotive power generation. The output power characteristics of the PEMFC are determined by the kinetics of the electrochemical reactions, internal electrical and ionic resistances and the crossover of reactants [18].

In this section, the principle of operation, the voltage-current characteristics of the PEMFC, the effect of current ripple and PEMFC dynamic performance are presented. These characteristics and properties must be considered while selecting the FC power converter (see Section 2.5).

#### 2.2.1 Principle of Operation

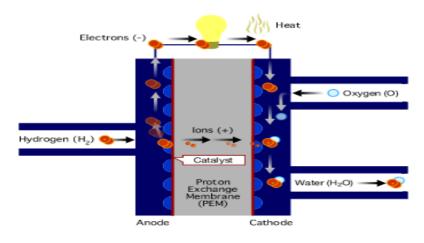

Fig. 2.1 illustrates the FC reaction for the PEMFC type. The hydrogen passes over the anode and with assistance of a catalyst the H<sub>2</sub> gas separates into electrons e<sup>-</sup> and hydrogen proton ions H<sup>+</sup>. The electrons cannot pass through the membrane and are forced to flow through an external circuit, consequently creating electricity, while positive ions can pass through the membrane and recombine with oxygen O<sub>2</sub> which flows through the cathode; the product of this recombination is pure water H<sub>2</sub>O [15, 18]. The chemical FC reaction process is given below [19]:

$$H_2 + \frac{1}{2}O_2 \longrightarrow H_2O + heat + electricity$$

(2.1)

The voltage produced by a single cell is usually less than 1.2 volt. For utility application multiple cells are bundled together in series to form a FC stack. The stack voltage is the

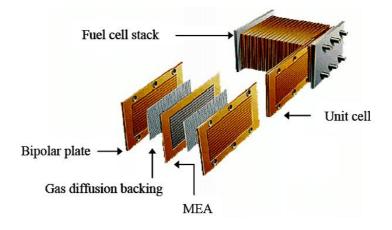

number of cells times the average voltage of the one cell. Fig. 2.2 shows the structure of the PEMFC stack [13].

Fig. 2.1 PEM fuel cell operation [20]

Fig. 2.2 PEMFC stack structure; MEA is a Membrane Electrode Assemblies [13]

# 2.2.2 Voltage-Current Characteristics of FC

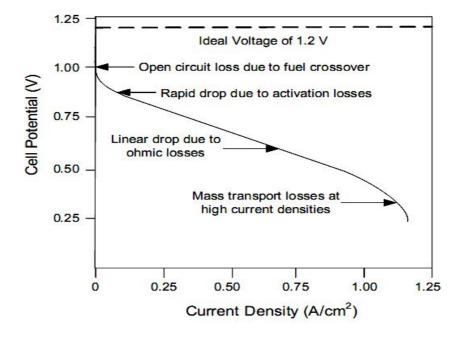

FC operation is similar to that of a battery in that a FC uses an anode and a cathode and the output is a  $DC^1$  voltage. But the output voltage of the FC exhibit significant degree of regulation with increasing current. Fig. 2.3 shows a typical voltage-current characteristic of a single cell. It can be seen that the cell voltage drops with current

<sup>&</sup>lt;sup>1</sup> However, the anode and cathode of the battery are metal/fluids while for a FC are gasses

density increase. This is due to three losses which are known as activation losses, ohmic losses, and concentration losses [21].

Fig. 2.3 Voltage-current Characteristic of FC [22]

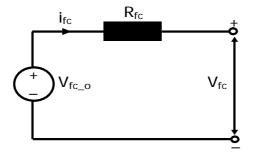

Activation losses are caused by the slowness of the chemical reactions taking place on the surface of the electrodes [22]. The ohmic loss is due to the resistance of the membrane, electrodes material, and the various interconnections. Operation of FC in the ohmic loss region is recommended since the voltage drop is proportional with the current density. In this region the FC can be represented as a Thevenin equivalent circuit consisting of a constant DC voltage source ( $V_{fc_o}$ ) with a series resistance ( $R_{fc}$ ), as shown in Fig. 2.4.

Fig. 2.4 Simplified FC equivalent circuit model

The ohmic resistance depends on the membrane characteristic and given as [18]:

$$R_{fc} = \int_0^{L_m} \frac{dx}{A_m \gamma_T}$$

(2.2)

where  $L_m$  is the thickness of membrane,  $A_m$  is the effective area of membrane, and  $\gamma$  is the conductivity of the membrane at the operation of temperature.

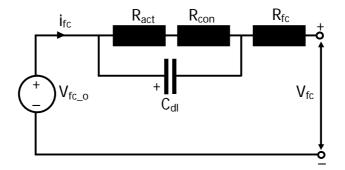

During the reaction process at high current density the change in the concentration of reactants results in mass transportation losses (or concentration losses), leading to a rapid drop in the voltage, as indicated in Fig. 2.3. Prolonged operation in this region leads to damage to the FC and has a very low efficiency [9]. The voltage drops due to the activation and concentration losses can be represented by the equivalent resistances  $R_{act}$  and  $R_{con}$ . Hence, the actual cell voltage  $V_{fc}$  is:

$$V_{\rm fc} = \Delta V_{\rm ohmic} - \Delta V_{\rm conc} - \Delta V_{\rm activ}$$

(2.3)

where  $\Delta V_{ohmic}$ ,  $\Delta V_{conc}$ , and  $\Delta V_{activ}$  are the voltage drop due to ohmic, concentration, and activation losses respectively.

As described in Section 2.2.1, the two electrodes of the PEMFC are separated by a membrane (see Fig. 2.1) which prevents the flow of electrons and only passes positive ions. The electrons flow from anode through the external circuit and recombine with the positive ions H<sup>+</sup> at the surface of the cathode. Hence, charged layers of opposite polarity are formed at the cathode and the electrolyte side of the membrane. Therefore, the cathode–membrane interface acts like a very large capacitor<sup>2</sup>, which is a store of electrical charge and energy [18, 23]. This is called the "double-layer" effect. A FC

$<sup>^2</sup>$  The PEMFC uses porous carbon electrodes; the extremely small pores measured in nanometres in such carbons give the material a very large active internal surface, thus the capacitance  $C_{\rm dl}$  is very large and can be in the order of several Farads.

dynamic model considering this effect is given in Fig. 2.5 as a first-order equivalent circuit [9, 24], where  $C_{dl}$  is the equivalent capacitance of double-layer.

Fig. 2.5 First-order FC equivalent circuit model

## 2.2.3 Constraints on FC Current

The FC is sensitive to any current ripple since it decreases the service life of the stack and impacts on the diffusion layer of the FC stack [25]. Moreover, at high ripple the FC operation could deviate from the ohmic region to the concentration region resulting in a possible shut down of the FC system. In addition to the ripple current, reverse current of the FC operation should be avoided and the load current should be limited to less than the maximum allowable current.

Therefore, it is preferable to employ a power conditioning unit that can avoid all the negative effects without adding protection circuits.

# 2.2.4 Dynamic Performance of the Ballard FC System

As the FC is the dispatchable generator in the system its dynamic response to load changes is vital to the design of the control system. Therefore, in this section experiments are described that have been carried out to establish of the steady-state and the dynamic performance of the Ballard Nexa<sup>TM</sup> 1.2kW PEMFC system. The results

have been used to upgrade an existing Matlab/Simulink model for later use with the whole FC converter model which is described in Chapter 4 (see Fig. 4.17).

# 2.2.4.1 Nexa FC Power Module Specifications

The Ballard Nexa FC is produced by Ballard Power Systems as an educational unit, and one such unit installed in the Projects Laboratory of the Electrical Power Group. It uses Ballard PEM technology and it is very suited for a diversity of power engineering purposes such as portable power source, back-up power generator, and stationary power supply system. It is able to produce 1.2 kW at a rated output voltage of 26 DC volts while the no-load voltage is 43V. The cell voltage is 0.6V at full load and 1V at light load. The rated gross current (which includes ancillary loads such as control board, pump, and cooling fan) that the module can produce is 46A and the maximum current is 60A. The ancillary loads consume 35 W at no-load and 250 W at full load [26]. Table 2.1 shows the major specifications of the Nexa Power Module.

| MAIN SPECIFICATIONS OF THE BALLARD NEXA FC POWER MODULE |                                            |  |

|---------------------------------------------------------|--------------------------------------------|--|

| Start-up process of the system                          | 10-30s from cold starting to running state |  |

| H <sub>2</sub> pressure ranging                         | 0.7-17.2 bar                               |  |

| Composition for H <sub>2</sub>                          | 99.99%                                     |  |

| Composition for O <sub>2</sub>                          | 21% (from air supply)                      |  |

| The maximum acceptable peak-peak ripple                 | 35% at rated current                       |  |

| current                                                 |                                            |  |

| Ambient temperature                                     | 3.3°C-30°C                                 |  |

| FC efficiency                                           | 38% at full load and 50% at light load     |  |

| Maximum fuel consumption                                | 18.5 Standard Litres per minute (slpm)     |  |

| Air flow consumption                                    | less than 90slpm at rated power            |  |

Table 2.1

Main specifications of the Ballard Nexa FC power module

In addition, this system requires an external 5V DC power supply during start-up and its protection circuit shuts it down if the stack voltage is less than 18V.

#### 2.2.4.2 Experimental Set-up

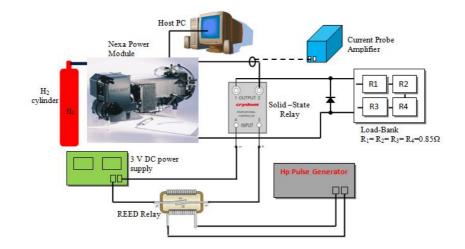

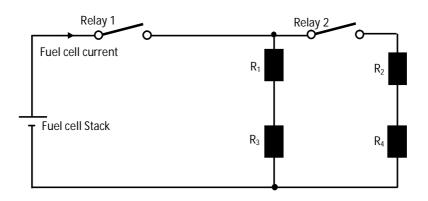

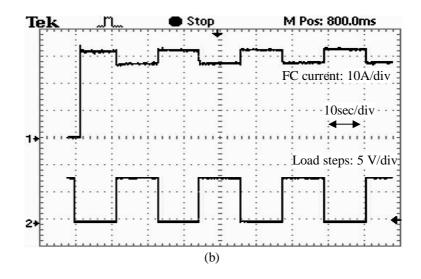

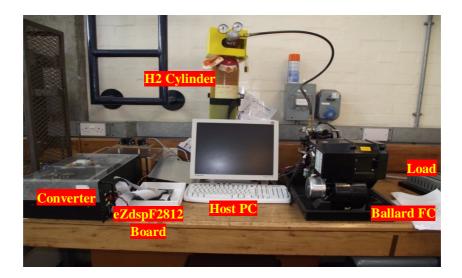

Since the exact dynamic response of the FC is important to select a proper controller design (see Section 4.4) for the proposed FC converter (see Chapter 3), an experiment was set up on the Nexa Power Module as shown in the block diagram of Fig. 2.6.

Fig. 2.6 The experimental set-up to evaluate the accurate dynamic response of the Nexa Power FC Module

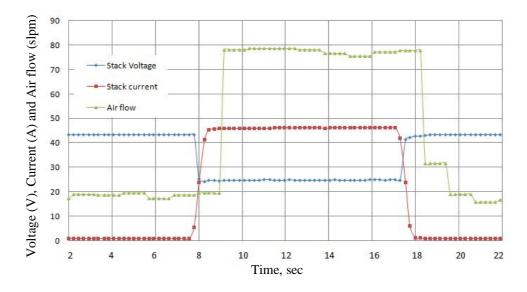

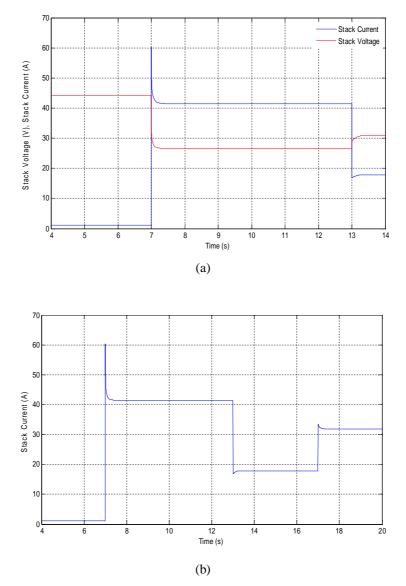

Initially, the experimental set-up was composed of the Nexa Power Module system, a low-inductance resistive load bank with four  $0.85 \Omega$  sections, a mechanical relay which was included with the Ballard system, and auxiliary equipment. The Ballard Nexa FC is equipped with a control board that transmits data via a communication serial port to a host PC for recording and displaying internal and external variables [26]. Using the "Nexamon OEM"<sup>3</sup> data log file the transient response characteristic of the Nexa system was obtained as shown in Fig. 2.7. These results show that the FC can respond to load changes from no-load to the full-load in 0.5 second. In the no-load state it was observed on the "Nexamon OEM Screen" that the FC voltage is 42V and a small current is drawn from the FC stack, about 1A, that is due to the ancillary loads.

<sup>&</sup>lt;sup>3</sup> Nexamon OEM is software programs to record and display different internal and external variables such as, stack voltage, stack current, fuel pressure, fuel consumption, stack power ....etc.

Fig. 2.7 Measured transient response of Nexa FC Power Module using "Nexamon OEM" data log file

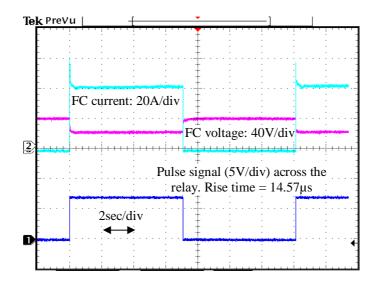

While adequate for general analysis the update time (0.2sec) of this data acquisition system is inadequate for measuring the transient response of the FC stack accurately. Therefore, an experiment was set up using fast-acting switches (Crydom D06D MOSFET solid-state relay) and high speed transducers (TM503 transducer) as shown in Fig. 2.6 to extract the exact dynamic response. A solid-state relay is used to independently change the resistive load across the FC output. The ON-OFF state of the Crydom relay is controlled using a HP pulse function generator (set on 71.42 mHz)<sup>4</sup>. The generated pulses are applied to the coil of a Reed Relay. The control terminals of the solid-state relay are connected to the output of a Reed Relay and the output of a 3V power supply. Three resistor sections were used, with two sections connected in series and paralleled with the third section, thus applying  $0.57\Omega$  across the FC to draw the nominal current of 46A.

Fig. 2.8 shows that when full-load is applied from no-load the gross stack current initially increases to about 1.3 times the nominal current (46A) before settling to the

<sup>&</sup>lt;sup>4</sup> The main feature of this function generator that provides very low frequency signals.

rated value in about 0.24 second. In comparison, the recorded response in the FC "Nexamon OEM" data log files (Fig. 2.7) doesn't show this current spike.

Fig. 2.8 Accurate transient response using experimental set-up in Fig. 2.6

The current peak is the result of charge double-layers on the electrodes of the cell. Depending on the density of the charges, electrons, and ions on the electrode and electrolyte surfaces a higher peak current can be generated.

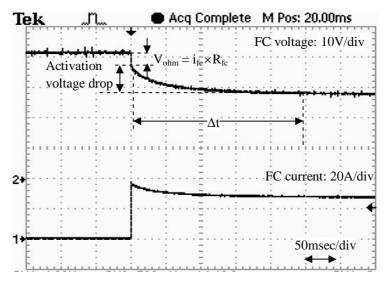

Further details of dynamic response of the Nexa FC are shown in Fig. 2.9.

Fig. 2.9 Dynamic Response of the FC shows the effect of the double-layer capacitor Cdl

It can be seen that when the load current steps up from 0A to 40A the FC output voltage shows an instantaneous change from 42V to 38V due to the ohmic resistance  $R_{fc}$ , but then decays further to the steady-state value (28V) after  $\Delta t = 0.24$ s. The latter is due to the activation losses, caused by fuel starvation [27].

It may be thought that the response in Fig. 2.8 and Fig. 2.9 demonstrate the ability of the PEMFC to follow rapid load variations. However, further tests at part–load, as described below, have shown that the double–layer effect is restricted to load changes from no–load after a sufficiently long period to re-establish the doubler–layer.

(a)

Fig. 2.10 Experiment set-up to evaluate the FC operation for different load demands: (a) equivalent circuit diagram and (b) measured FC current results

Using the test set–up in Fig. 2.10a the response of the FC to small variations in load demand while delivering a substantial proportion of the nominal current was investigated. Initially, when applying 70% load from no–load, the current peak present, but at subsequent cycling of the load by 10% the peaks are absent (Fig. 2.10b).

Due to the chemical reaction inside the FC stack, it is clear that the FC needs time to recover to the steady-state voltage when the load changes. The FC cannot keep the output voltage constant. Hence, a power conditioning unit, such as DC-DC converter, is necessary to obtain a constant voltage. To improve the dynamic response of the FC, avoid the fuel starvation problem, maintain constant output power for the FC, and absorb the surplus energy during transient load drops, an ultracapacitor energy buffer is needed (see Section 2.4.2 for more detail about the FC-UC interaction).

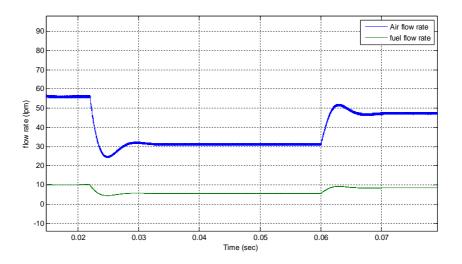

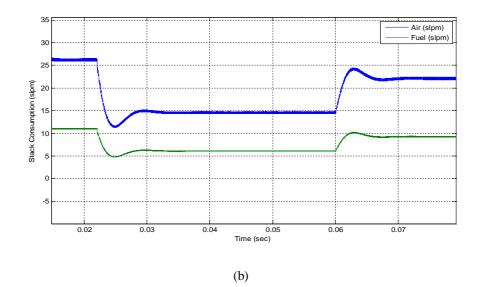

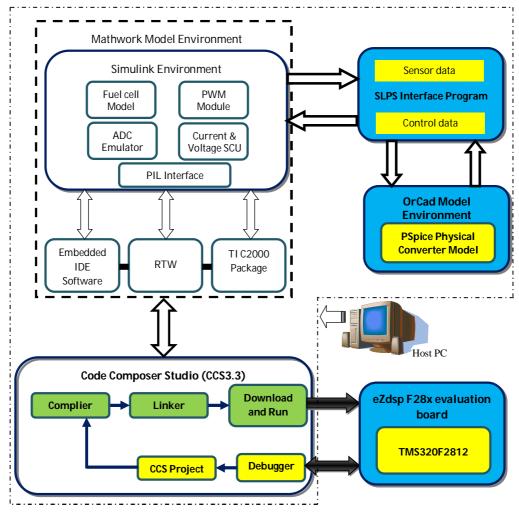

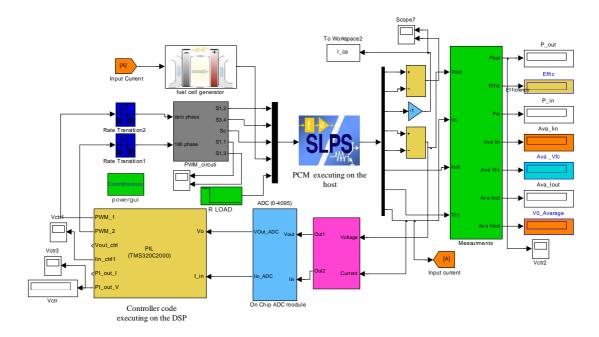

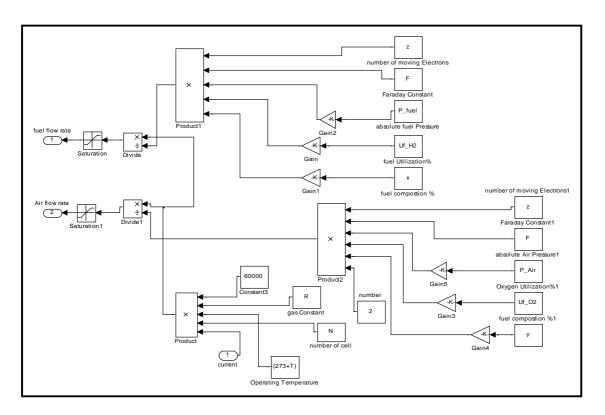

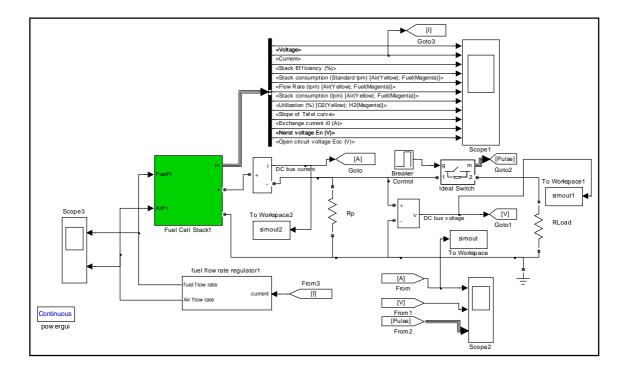

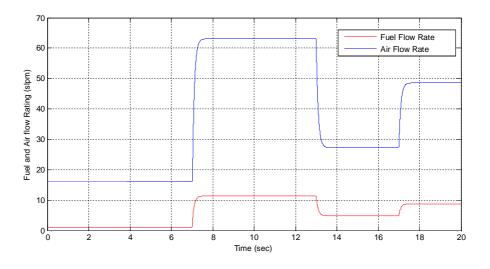

#### 2.2.4.3 Dynamic Model of the PEMFC

The dynamic model of PEMFC used in this study is based on an existing Matlab model with added flow rate regulators to control the fuel and air utilization (see Appendix A). The load conditions of the experiment were applied to the FC model as illustrated in Appendix A and by comparing the responses to load changes the unknown parameters for the real FC were obtained. As indicated in Appendix A, the Simulink results show that the modelling matches well with the experimental set-up. This model has been integrated with the PSpice model of the FC converter (see Chapter 3) using the SLPS simulator to develop the FC control system and algorithms, as will be described in Chapter 4.

## 2.3 Ultracapacitor Energy Buffer

Ultracapacitors (UCs) or Supercapacitors, also called "electric double layer" capacitors, are electrochemical capacitors with very high capacitance values<sup>5</sup> and very large energy density compared to the conventional capacitors. The same basic principle of conventional capacitors applies to ultracapacitors, but with UCs the electrodes have a much larger surface area and thinner dielectrics to achieve larger capacitances [13, 28]. Compared with batteries, UCs have a longer lifetime<sup>6</sup> and higher power density. However, UCs have lower energy density than batteries, which in most cases determines the viability of their employment in a particular high power application. As indicated in Chapter 1, storage devices are introduced in microgrids in order to secure their power quality, power regulation and to offer ancillary services during transient periods.

This section briefly describes the operational principle and the electrical characteristic of the UC energy buffer. This section also introduces a developed equivalent circuit model for an UC that takes into account the most important UC characteristic, such as the non-linear voltage-capacitance dependency.

# 2.3.1 Principle of Operation

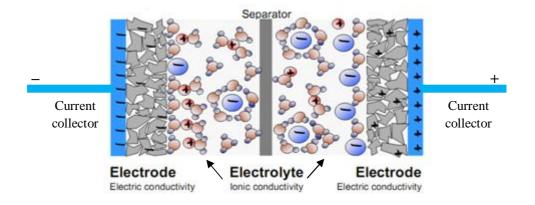

An ultracapacitor comprises two electrodes, a separator, and an electrolyte, as depicted in Fig. 2.11. In an UC, energy is stored by the separation of positive and negative charges at the interfaces between the electrode and the electrolyte. This is called the double–layer capacitor phenomenon [29, 30].

<sup>&</sup>lt;sup>5</sup> For the Maxwell Boostcap<sup>TM</sup> technology capacitance values reaching up to 3000 Farads for a single cell with voltage rating up to 2.7V.

<sup>&</sup>lt;sup>6</sup> Compared to the batteries, the UCs have a considerably longer cycle life because there are no chemical reactions during charging and discharging.

Fig. 2.11 Principle of operation of Ultracapacitor [29]

Three main factors determine the amount of energy that can be stored in an UC: the separation distance between the electrodes, the surface area of electrode, and insulating layers which are separating the electrodes [31]. The two electrodes consist of a porous nanostructure made of carbon materials to provide a larger surface area than conventional capacitors. To interface the electrodes with the terminal connection of the UC, current collectors with a high conductivity are employed. The electrodes (or the anode and cathode) are separated by a thin isolation separator which allows the ions to move freely and blocks the electrons [32]. The voltage rating for a single cell of the UC is determined by the electrolyte properties. Most types of electrolyte, such as organic electrolytes, generally give a rated voltage less than 3V for a single UC cell. This voltage level is very low and therefore UC cells are connected in series to achieve a higher voltage level by forming what is known as a UC module. However, this of course increases the equivalent series resistance (ESR) of the UC (for the BMOD0165 module the ESR is about  $6.3 \text{m}\Omega$ ) and therefore it is desirable that the ions have high mobility in the electrolyte to reduce the ESR of the UC module [33]. Due to the cell's leakage current there is the possibility of an imbalance in the distribution of voltages across the UC cells [13]. Therefore, active or passive balance circuits are essential to protect each cell from overvoltage.

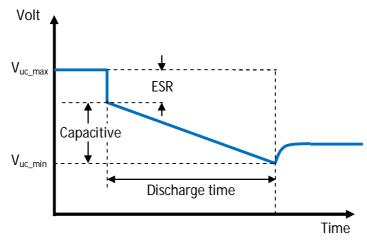

## 2.3.2 Electrical Characteristic of Ultracapacitor

The performance of an UC can be characterised by its terminal voltage during discharging and charging at different current rates. Unlike batteries, the parameters of the UCs depend on the voltage, rather than the current, since the charge stored is based on the capacitance and the voltage. An UC's voltage profile has capacitive and resistive components. The capacitive component indicates the charge or discharge energy within the UC. The resistive component represents the voltage drop due to the internal ESR of the UC [13]. The voltage profile of the UC during constant current discharge is illustrated in Fig. 2.12.

Fig. 2.12 Constant current discharge profile of the UC

Compared to the batteries, UCs can deliver 10–20 times more power and they can be discharged and charged very fast [30]. This is very important feature in order to match the slower power output of the FC and provide the required power for the DC load or AC grid to improve the performance characteristics of the FC-UC DC microgrid. However, this feature will only be of use if the DC-DC converter has been selected appropriately.

#### 2.3.3 Dynamic Modelling of the Maxwell Ultracapacitor

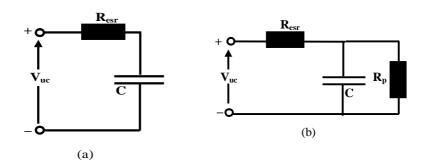

In order to evaluate the UC system performance, it is necessary to develop a dynamic model describing the behaviour of the UC that can then be integrated with a model of the power electronics converter. A number of UC models have been proposed in the literature [34-38]. The UC can be modelled as an ideal capacitor C in series with a resistor  $R_{esr}$ , as shown in Fig. 2.13a. However, this is a simplified model for the UC and it is not appropriate if a fast transient response is sought. A first-order model for an UC including the self-discharge effect<sup>7</sup> is shown in Fig. 2.13b [37]. It consists of three components, which include a voltage–independent capacitance C, an equivalent series resistance  $R_{esr}$ , and a self-discharge resistance  $R_p$  which models the self-discharge effect [38].

Fig. 2.13 Different equivalent circuit models for the UC: (a) RC model (b) first-order dynamic model [37]

It can be observed from Fig. 2.13 a and b that unlike the FC equivalent circuit, the UC model is a purely passive model, with no voltage or current sources.

The above UC equivalent models assume a linear behaviour for the UC. However, the UC exhibits a non-linear voltage characteristic and its dynamics are related to the temperature, the frequency of the current and the voltage across the capacitance [35].

<sup>&</sup>lt;sup>7</sup> The electrolyte between the electrodes passes a small amount of leakage current which causes the voltage of a charged UC to decay over time. This phenomenon is known as the self-discharge effect.

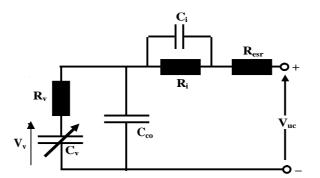

Therefore, more accurate model consider the non-linearity behaviour of the UC was proposed in [39]. Based on that model, an equivalent circuit model of UC energy buffer is introduced in this section that models the non-linear voltage-capacitance dependency of the UC using Matlab/Simulink. Fig. 2.14 shows the modified equivalent UC circuit model.

Fig. 2.14 Equivalent circuit used to model the Maxwell BMOD0165 ultracapacitor

As can be seen this equivalent circuit consists of 6 components:  $C_v$  is the voltage– dependant capacitance<sup>8</sup>,  $C_{co}$  is a constant capacitance,  $R_v$  is the ESR DC resistance,  $R_i$ represents the ionic resistance in the electrolyte, and  $C_i$  represents the capacitance utilised to cancel the effect of  $R_i$  at high frequencies.

To take into account the capacitance variation in respect to the voltage, the main capacitance C for the UC is represented as the sum of a constant capacitance  $C_{co}$  and non-linear capacitance  $C_v = K_v V_v$ , so that the total capacitance given as

$$C = C_v + C_{co} \tag{2.4}$$

where  $K_v$  is a non–linear function of  $V_v$

The voltage-capacitance data was extracted from the test cycle curve for a Maxwell BMOD0165 ultracapacitor as provided by the manufacturer [29, 40, 41], and is used in

<sup>&</sup>lt;sup>8</sup> The capacitance-voltage dependency is due to reduction in the distance separating the charges at the cathode–separator interface with an increase in voltage, leading to an increase in capacitance as a consequence.

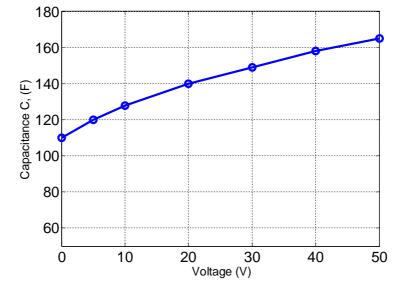

the proposed model as shown in Table 2.2. The obtained voltage-capacitance relationship is depicted in Fig. 2.15.

| MAIN SPECIFICATIONS OF THE MAXWELL BOOSTCAPTM UC MODULE |                                    |  |  |  |

|---------------------------------------------------------|------------------------------------|--|--|--|

| Nominal Capacitance C                                   | 165 F                              |  |  |  |

| Rated Voltage V <sub>uc</sub>                           | 48V                                |  |  |  |

| Max continuous Current I <sub>uc_max</sub>              | 98 A                               |  |  |  |

| Leakage current                                         | 5.2 mA                             |  |  |  |

| Operating Temperature range                             | $-40^{\circ}$ C to $+65^{\circ}$ C |  |  |  |

| Energy Available E <sub>uc</sub>                        | 54 Wh                              |  |  |  |

| Number of cell N <sub>uc</sub>                          | 18                                 |  |  |  |

| Capacitance of each cell C <sub>uc</sub>                | 3000 F                             |  |  |  |

| Constant Capacitance $C_{co} = (2/3) \times C$          | 110F                               |  |  |  |

| ESR, DC R <sub>v</sub>                                  | 6.3 mΩ                             |  |  |  |

| ESR, AC                                                 | 5.2 mΩ                             |  |  |  |

| $C_i = C_{co}$                                          | 110 F                              |  |  |  |

TABLE 2.2

Fig. 2.15 UC capacitance as a function of the voltage

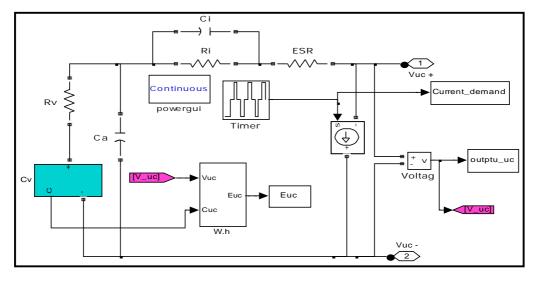

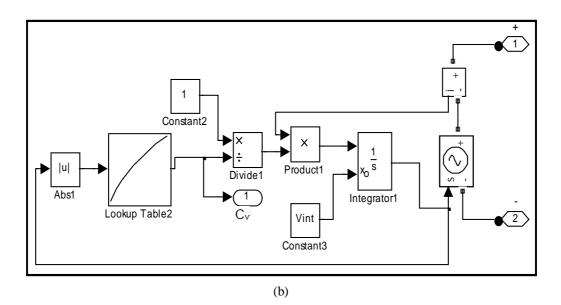

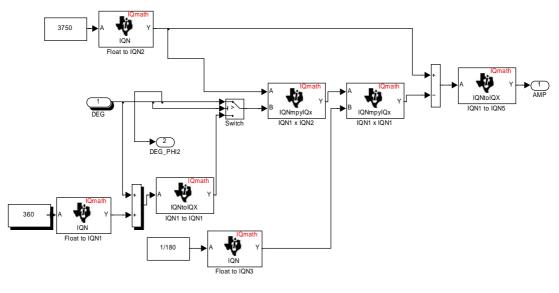

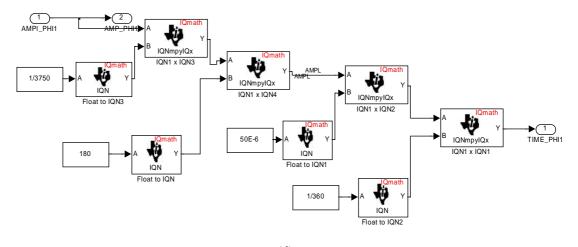

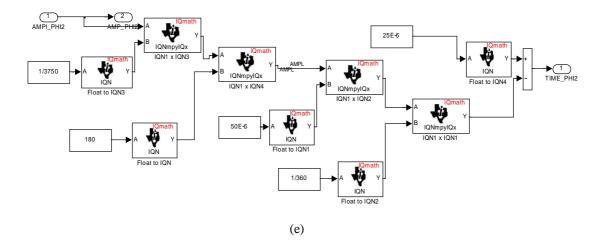

The equivalent circuit has been modelled in Matlab/Simulink as shown in Fig. 2.16a.

(a)

Fig. 2.16 Simulink block diagrams of (a) the UC model , (b) the details of block C<sub>v</sub>, which is represent the non-linear capacitance

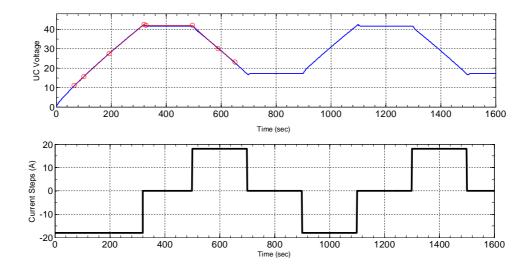

Fig. 2.16b shows the Simulink block diagram which is used to represent the non-linear voltage-dependency of the capacitance for the UC. Fig. 2.17 illustrates the simulation results which is represents the voltage behaviour of the UC in the time range of seconds in response to charge or discharge action at constant current (in order of 20A). Measured results in [40] and modelled voltage characteristics are compared which show that the proposed model very closely matches the measured results of BMOD0165 ultracapacitor.

Fig. 2.17 Measured (red) and modelled (blue) results show the voltage characteristic of the UC based on the Maxwell 6-step evaluation test (black) at 20A

Fig. 2.18 show the modelled charge characteristics of the Maxwell BMOD0165 UC at different charge current values. It can be seen that the voltage increases non-linearly with charge time. At a large charge current, the rated voltage increase is much higher than at a small current value.

Fig. 2.18 Simulation results of the modelled charge characteristics for the Maxwell BMOD0165 UC

In Chapter 6 the Simulink model is interfaced with the model of an isolated bidirectional DC–DC converter, simulated in PSpice via the SLPS interface, to achieve an accurate dynamic performance for the whole UC converter model.

#### 2.4 Configurations of Fuel Cell–Ultracapacitor DC Microgrid

#### 2.4.1 Overview of Configurations

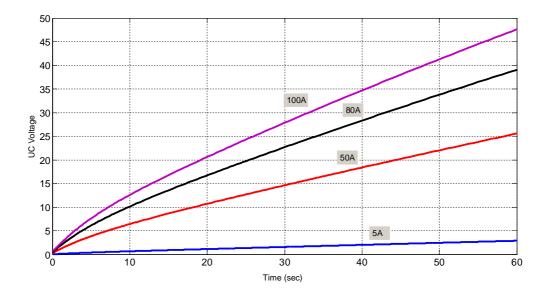

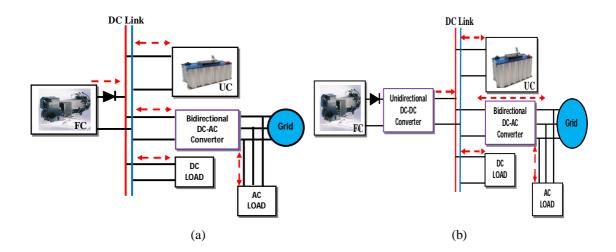

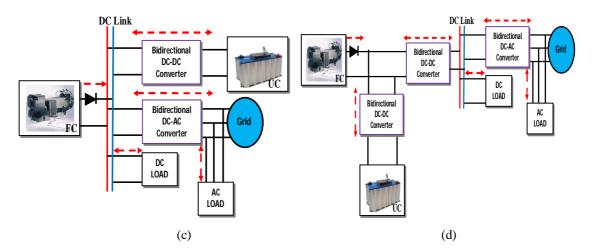

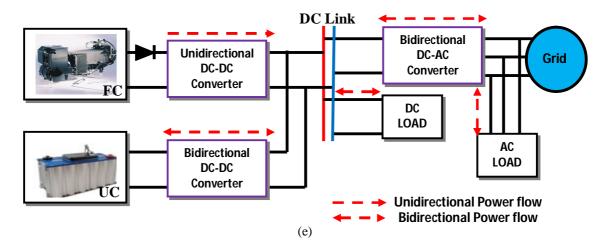

To compensate for the sluggish response of the FC in supplying the amount of power demanded by the load, a fast response energy buffer such as ultracapacitor is needed. Several configurations have been proposed to interface the ultracapacitor to the FC system. As indicated in Chapter one, to simplify the design of the DC–AC converter of DC microgrid a DC link voltage between 600 and 800V is required. Fig. 2.19 shows different configurations of the fuel cell–ultracapacitor (FC–UC) DC microgrid.

In the first configuration, shown in Fig. 2.19a, the FC and the UC are connected directly in parallel to the DC link forming a passive FC–UC hybrid connection [42, 43]. With this configuration no converters are employed for the FC or the UC. Hence, low losses and low cost can be achieved. The main problem associated with this configuration is that no direct control is included for the FC current and UC charging/discharging and the UC energy cannot be fully used. In addition, the impedance mismatches between the parts of this configuration lead to starvation problem and heavy mechanical stresses on the FC system [18, 44]. To control the current of the FC, an active FC–UC hybrid configuration based on connecting a unidirectional DC-DC converter between the FC and the DC link is illustrated in Fig. 2.19b [27]. With this configuration a rapid rise of the FC current is avoided and thus prevents the fuel starvation. In contrast to the first configuration in Fig. 2.19a, a low–voltage FC source can be utilised. However, since the UC is connected directly to the DC link it must have a high voltage rating. Also, the

power between the UC and the DC link is uncontrolled, therefore this configuration is not a good solution for power management between the FC, the UC, and the DC link.

Fig. 2.19 Different UC positions to improve the FC dynamic response and manage the power flow in the FC–UC DC microgrid: (a) passive FC–UC hybrid connection (b) active FC–UC hybrid connection with

FC unidirectional converter (c) active FC–UC hybrid connection with UC bidirectional converter (d) parallel–connection of FC and UC through individual DC–DC converters with UC bidirectional converter connected directly to the FC(e) parallel–connection of FC and UC through individual DC–DC converters with UC bidirectional converter connected to the DC link

The UC can be connected to the DC link through a bidirectional DC-DC converter to maintain the charging and discharging of the UC and to regulate the DC link voltage, as depicted in Fig. 2.19c [45-47]. In this configuration, the UC energy buffer is not connected directly to the DC link and therefore a low-voltage UC can be employed. This configuration is widely used for hybrid electrical vehicle applications due to its simplicity and good power flow controllability [47, 48]. However, for the present application this configuration requires a high-voltage FC to fulfill the DC link voltage level (the DC link voltage is up to 650V), which is not a good solution because of the

FC cost and reliability<sup>9</sup>. Furthermore, the FC is vulnerable to any rapid dynamic operation of the load since no converter is included to limit the FC current. Therefore, this configuration is not preferable for application in high-voltage power distribution systems.

Another solution to improve the dynamic response of the FC can be obtained by parallel connection of the FC and UC through two different DC-DC converters as depicted in Fig. 2.19d and e. In these configurations the UC converter is connected either to the low-voltage side, as shown in Fig. 2.19d, or to the high-voltage DC link side, as demonstrated in Fig. 2.19e. However, the latter structure provides more control flexibility compared to the first structure. This is because the UC converter in Fig. 2.19d is required to operate with wide input and output voltage variations and it cannot regulate the output voltage since the converter is connected directly across the FC. Nevertheless, both structures can be considered as the best choices for optimal power utilization. With both configurations it is possible to select a low-voltage FC and UC source without having to increase the FC or UC stack size. In addition, they are give a

<sup>&</sup>lt;sup>9</sup> FCs with high output voltage require a large number of cells in series. If a single cell fails open circuit, the entire stack stops functioning because the current flow is interrupted. This results in a lower FC reliability.

great degree of freedom in power flow controllability [46]. Furthermore, with the configuration in Fig. 2.19e the FC and UC are decoupled from the DC bus so that the input currents can be limited to the acceptable level during rapid transient operation while sustaining the DC link voltage at the required level even for wide input voltage variations. However, with two–converter configurations high losses associated with each converter are expected. Therefore, based on the configuration in Fig. 2.19e, an investigation for efficient DC-DC converter topologies with respect to electrical characteristics of the FC and UC are presented in this Chapter.

#### 2.4.2 Power Flow Management and Control Strategy

Based on the energy conversion architectures described in the last section, the purpose of the hybridisation between the FC and UC in a DC microgrid is to achieve the following:

- 1. improve the FC output power response,

- 2. supply power to the fluctuating load whilst taking into account the low FC dynamics, and

- 3. recover the power generated by the load and store it in the energy storage.

In this way, the whole system would be more efficient and reliable and gives the mechanical devices of the FC sufficient time to adjust, leading to FC operation under more reliable conditions.

The studied configuration of the FC–UC DC microgrid, shown in Fig. 2.19e, has various operational modes according to the conditions of the FC and the UC during autonomous or grid-connected mode. This configuration can be represented as an equivalent circuit as depicted in Fig. 2.20. In this figure the fuel cell–unidirectional DC–DC converter system (FC–UDC) and the ultracapacitor–bidirectional DC–DC converter

system (UC–BDC) in Fig. 2.19e are represented as two DC constant power supplies, delivering the required power to the DC load during autonomous operation.

Fig. 2.20 An equivalent circuit of the FC-UC DC microgrid during autonomous operation mode

In this operation the following modes are possible:

- During power demand transient, the UC energy storage delivers the transient power  $\Delta P_{load}$ . Hence,  $P_{uc} = \Delta P_{load}$ .

- In constant low–power demand operation, the FC will deliver power to the load and charge the UC storage to recover charge lost during the transient power demand operation. Hence,  $P_{fc} = P_{load} + P_{uc}$ .

- In constant power demand operation when the UC is fully charged, FC will deliver the power to the load. Hence,  $P_{fc} = P_{load}$ .

- In the constant high–power demand operation (i.e. load demand > the power delivered by the FC), the FC and UC will deliver the power to the load simultaneously. Hence,  $P_{fc} = P_{load} P_{uc}$ .

- In transient energy recovery operation, such as the sudden transition from the load to no-load, the surplus power will be absorbed by the UC storage. Hence,  $P_{uc} = -\Delta P_{load}$ .

For grid–connected operation, the same modes as above are valid but two more possible modes exist:

- In transient energy recovery operation, if the UC is fully charged the surplus power will be absorbed by the utility gird.

- At constant high–power demand, if the load demand is higher than the maximum power that can be supplied by the FC and UC converter systems, the utility grid will supplement the load power.

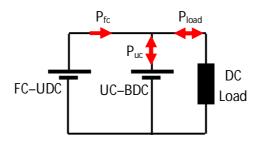

To manage the power flow efficiently taking into account the above modes of operation, a control strategy is needed. A number of control strategies have been proposed for the power management of FC–UC hybrid systems [13, 43-47, 49, 50]. The control strategy should manage not only the power flow between the microgrid parts but it should also control the SOC for the UC and maintain the DC link voltage. Hence, the main role of the control strategy of the DC microgrid system can be summarised as depicted in Fig. 2.21.

Fig. 2.21 The main role of the control strategy for the FC-UC DC microgrid

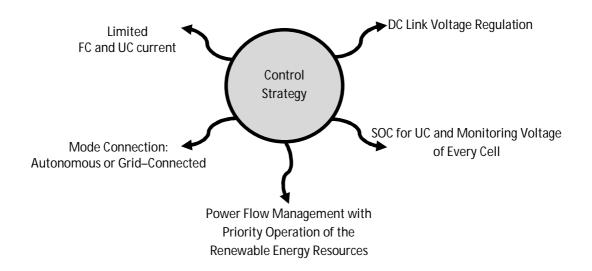

In this section, a control strategy for the FC–UC DC microgrid is developed for the power management of the FC and UC sources supplying the load during autonomous operation. Fig. 2.22 shows the basic schematic diagram of the proposed power

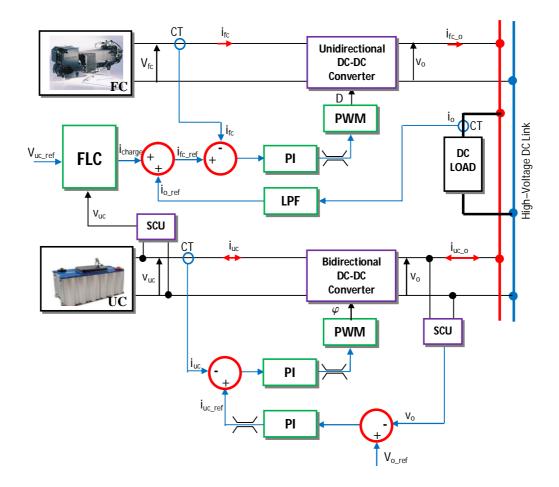

management system. In this management system the FC only supplies the base power, while the UC will supply the transient power to the load and regulate the voltage of the DC microgrid. In addition the power management is employed to control the SOC of the UC. The structure of the developed system is composed of the unidirectional converter, bidirectional converter, FC, UC, and closed loop control circuit. The closed loop control circuit comprises a fuzzy logic controller (FLC), a load current detection loop, two inner current loops and an outer voltage loop. The purpose of each control loop is described below:

- Load current detection loop: as indicated in Fig. 2.22, a low-pass filter (LPF) is used to prevent load transients from directly affecting the operation of the FC. Thus, FC responds smoothly to the load demand.

- FC inner current loop which is used to control the input current to the unidirectional converter in order for the FC to deliver the steady-state or average power required by the load and the UC.

- FLC which is utilised to maintain the SOC of the UC within the allowed operating voltage range and to drive the FC current loop with the required charge current reference.

- Voltage control loop to regulate the DC link voltage

- UC inner current loop to limit and control the UC current.

Fig. 2.22 Control scheme for the FC-UC DC microgrid

From the system structure shown in Fig. 2.22, it can be seen that the FC current loop is driven by two current references  $i_{charge}$  and  $i_{o_ref}$  to control the FC converter. The sum of these generate the reference current  $i_{fc_ref}$  which is compared with the actual FC current and the error signal is processed by the FC current controller to control the converter via the duty ratio. In order to eliminate interaction between the FC control loop, the UC control loop and the load current detection loop, a decoupling between the loops must be achieved. For example, to guarantee a smooth response for the FC whilst compensating any power deficiency due to load transients the outer voltage loop must be designed with a higher bandwidth than the cut-frequency of the LPF and the FC current loop. In order for the FC to track the load current demand, once transient

changes have been eliminated, the FC current loop should have a higher bandwidth than the cut-frequency of the LPF.

As mentioned above it is necessary to monitor the UC voltage to control the SOC. When the UC voltage approaches the maximum or the minimum limiting voltage, the FLC will adjust the required current reference  $i_{charge}$  and then compared it with the FC current to control the FC converter.

The power management system for a DC microgrid is described here only briefly to clarify how the power flow is managed in the FC–UC DC microgrid. However, further analysis and implementation of the developed control strategy is required.

#### 2.5 Topologies of Fuel Cell and Ultracapacitor Power Converters

In the parallel-connection topology of the FC-UC DC microgrid in Fig. 2.19e, the FC and UC sources are supplying power to the DC bus through two different DC–DC power converters, which are unidirectional and bidirectional respectively. These two converters are the key elements that interface the FC and UC to the rest of the DC microgrid system. A unidirectional converter is preferable for the FC to prevent reverse power, while a bidirectional converter is necessary for the UC to sustain the charging and discharging states of the UC. The main objective of these converters in the FC-UC microgrid is to balance the power flow among the FC, the UC, and the DC link.

As indicated in Sections 2.2 and 2.3, FCs and UCs are typically generating low–voltage DC power. Therefore, step-up DC–DC converters are needed to satisfy the voltage level of the DC link of a DC microgrid. Furthermore, galvanic isolation from the output of FC and UC converters is very desirable where other generators of the DC microgrid system share the same DC bus. Moreover, a converter configuration that combines high

reliability, high efficiency, a high conversion ratio, as well as a low ripple current and low cost is sought.

In addition to the above requirements, the design and selection of the converter should take into account the dynamic response of the FC and UC. Therefore, this section presents an overview of several DC-DC converter configurations that can meet the above requirements for the FC and UC.

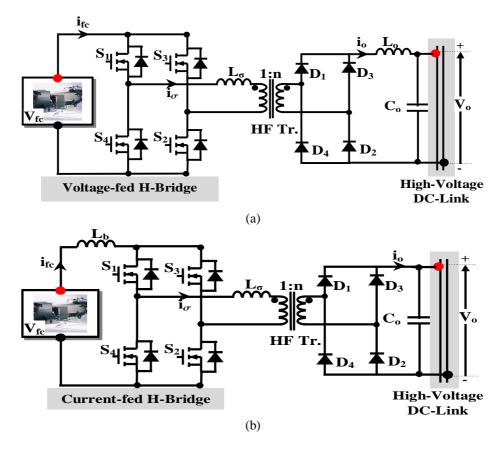

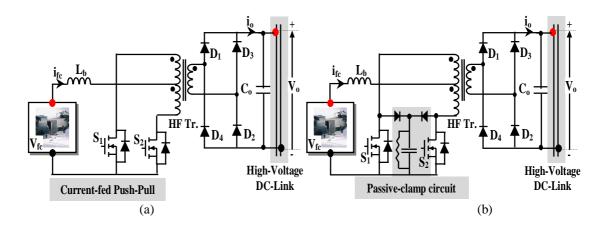

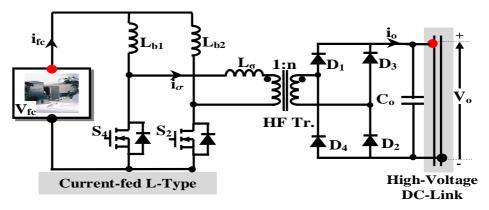

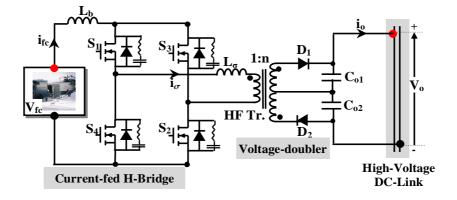

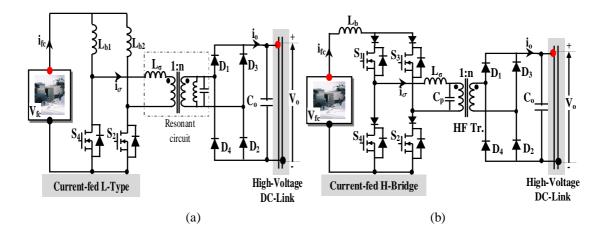

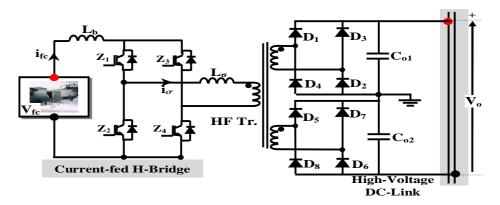

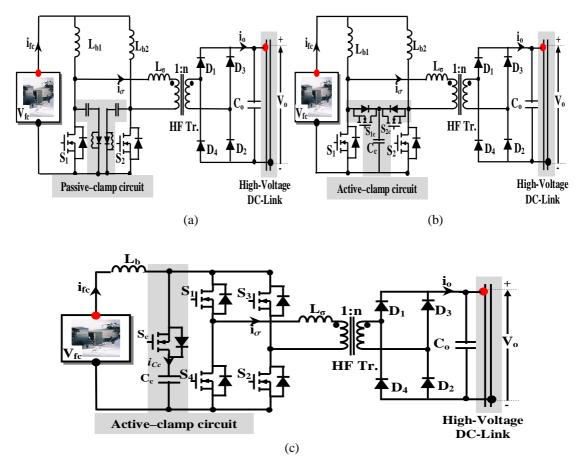

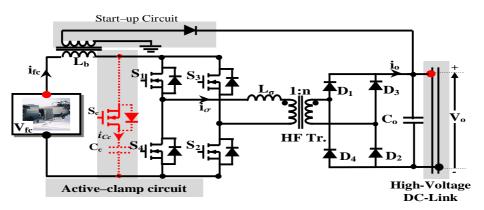

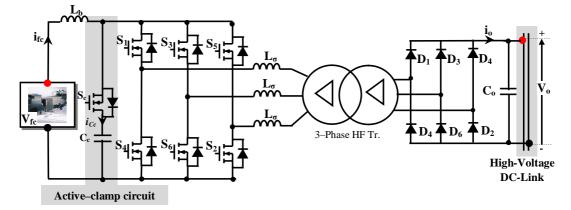

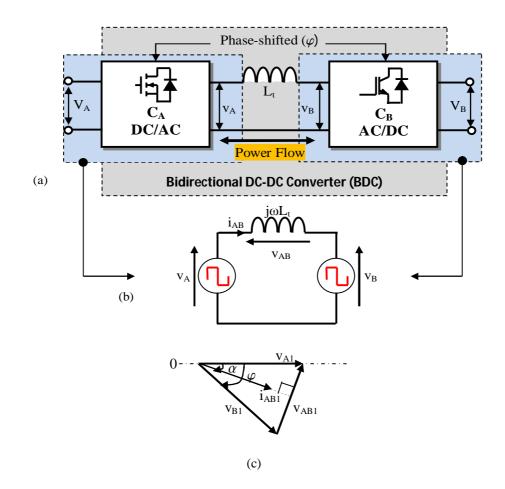

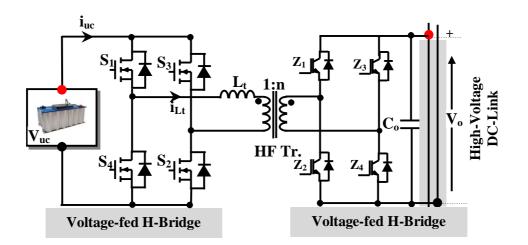

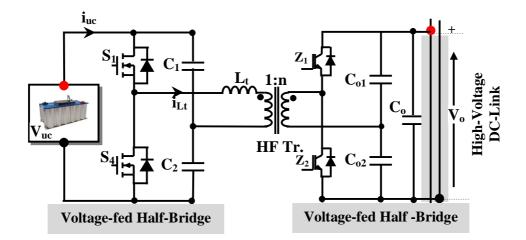

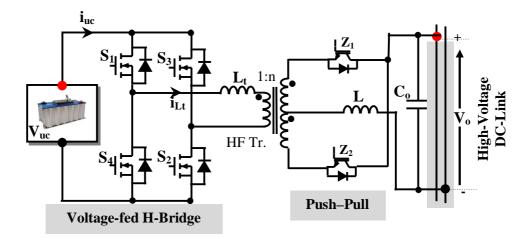

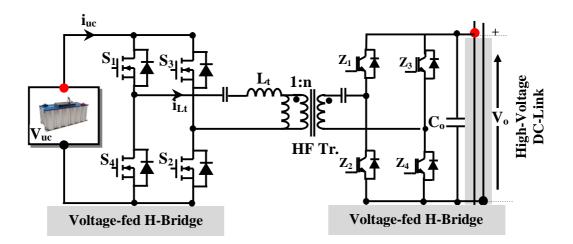

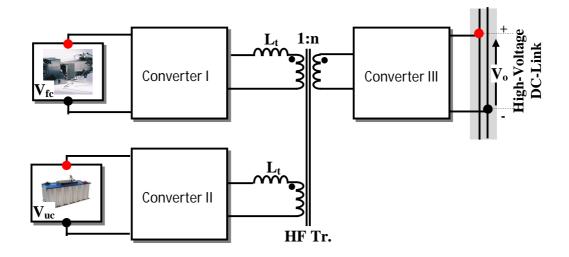

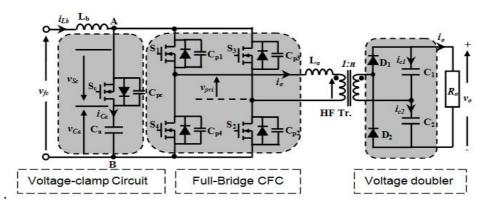

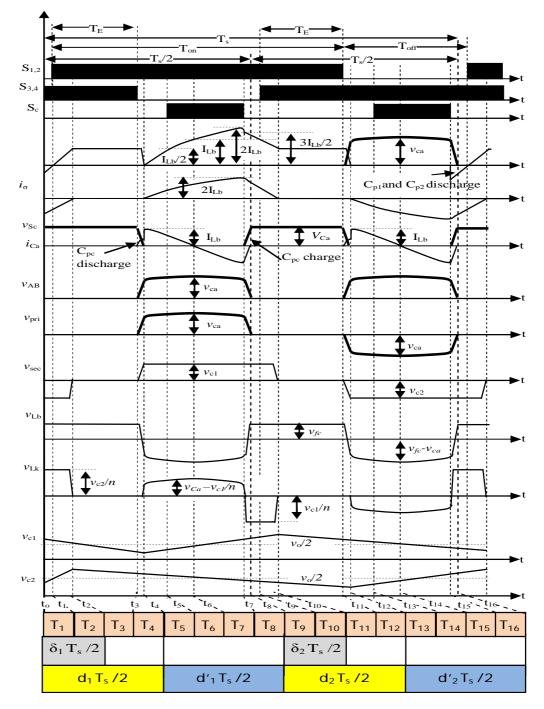

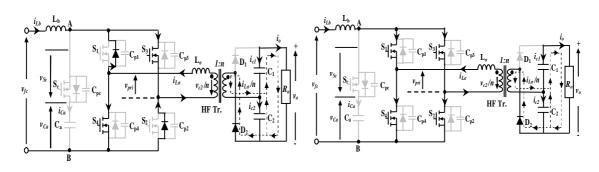

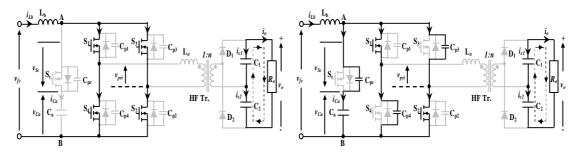

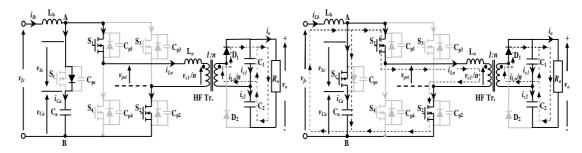

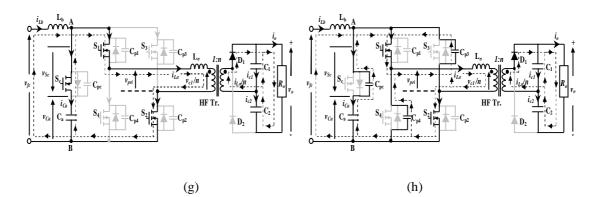

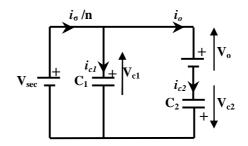

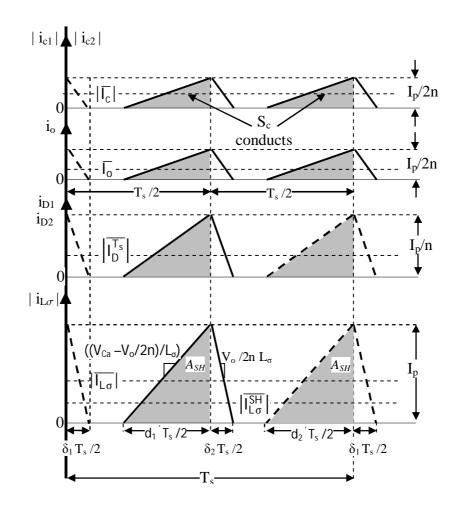

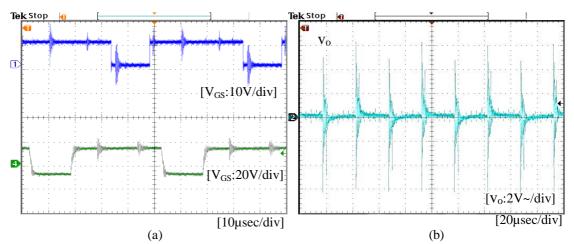

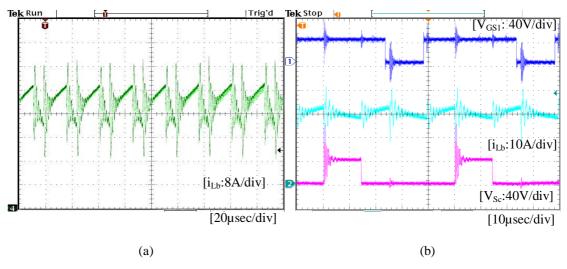

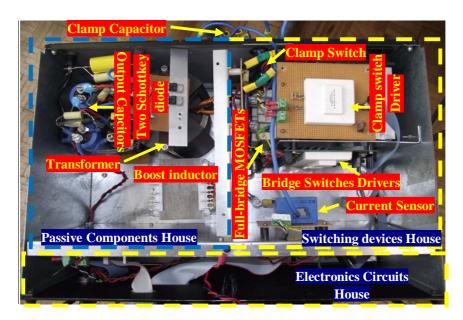

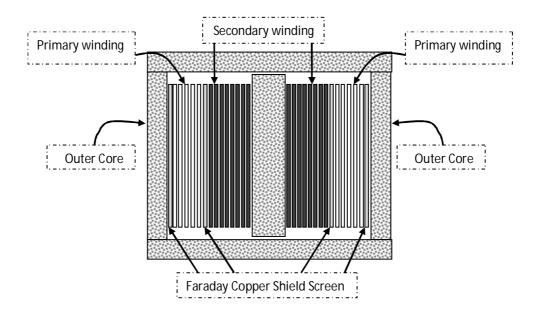

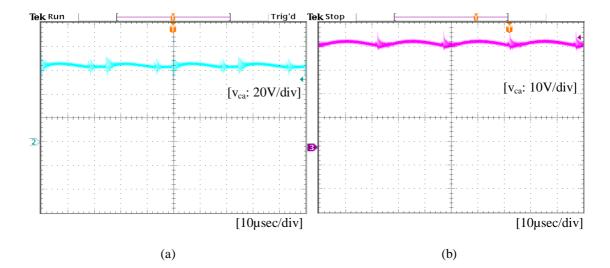

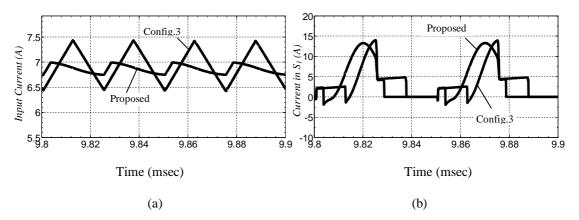

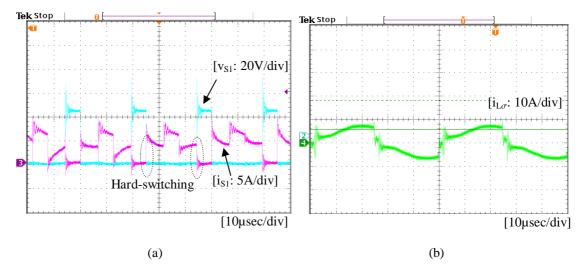

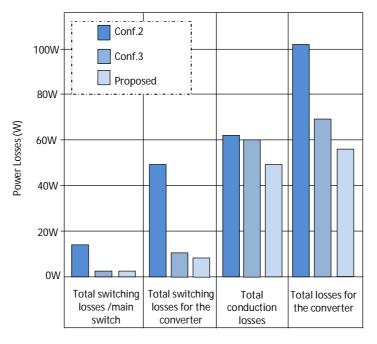

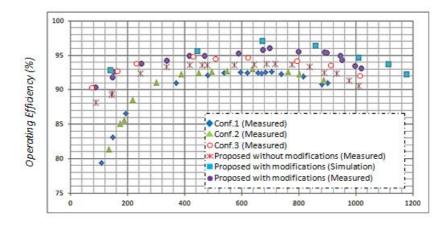

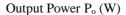

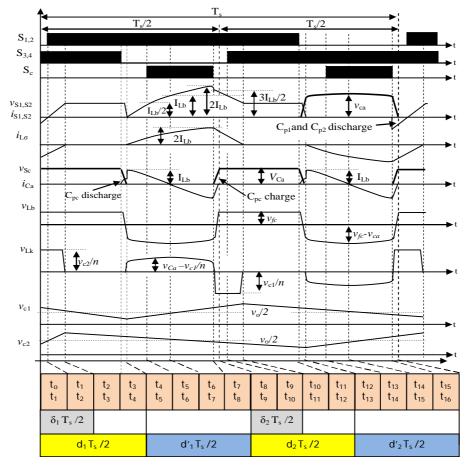

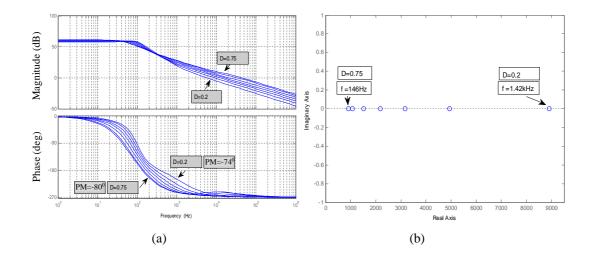

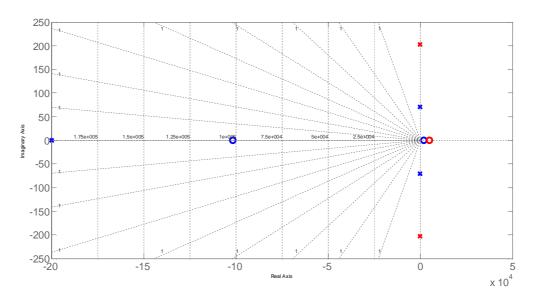

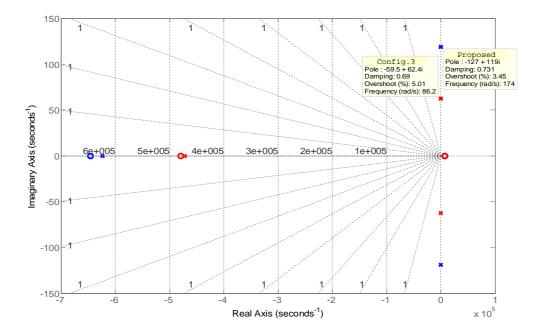

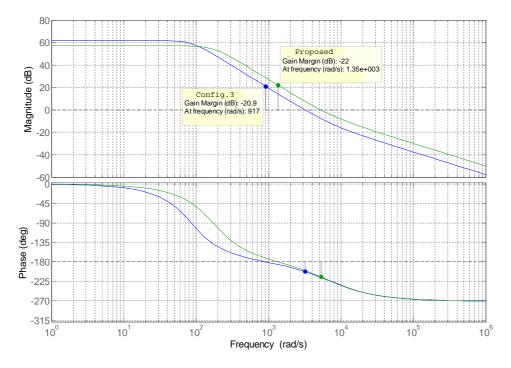

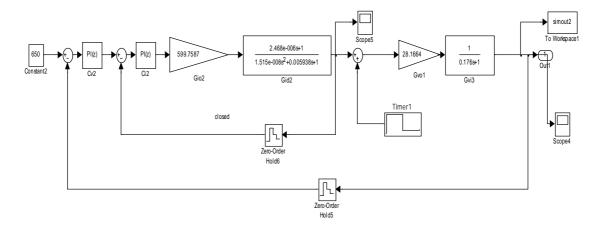

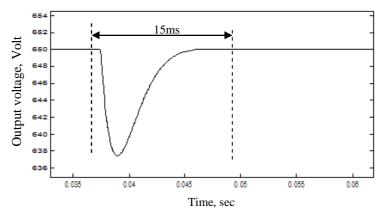

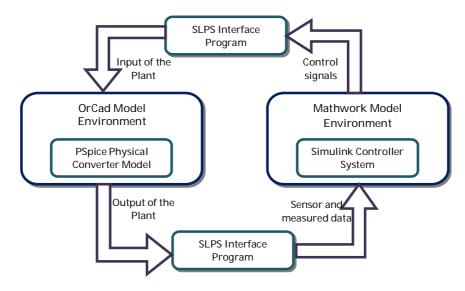

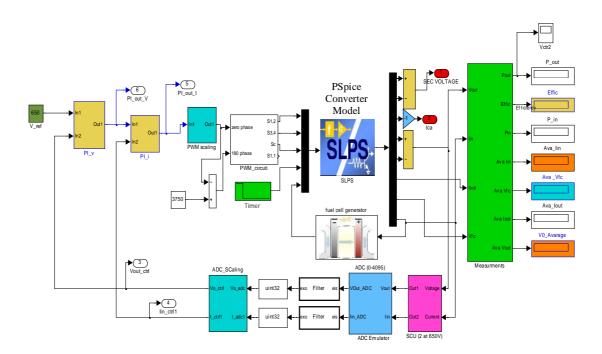

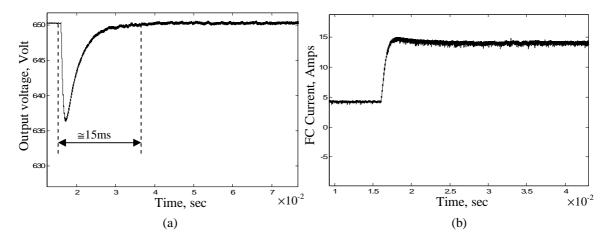

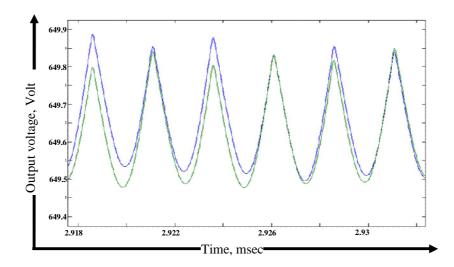

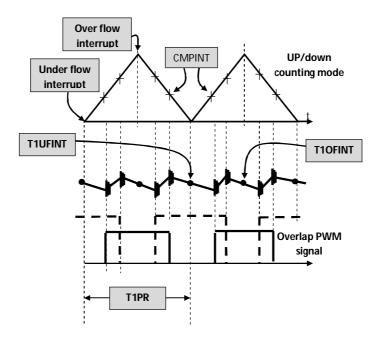

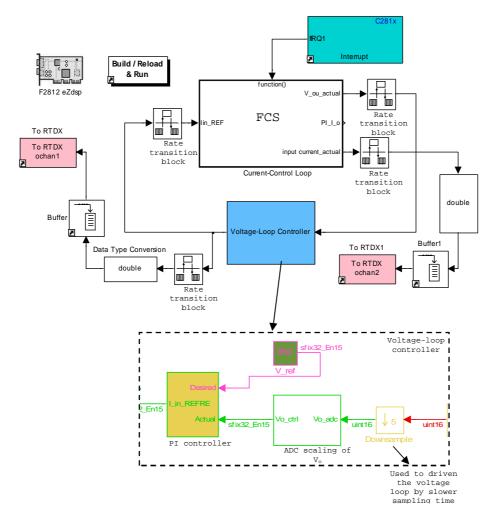

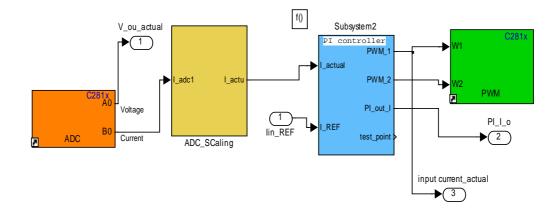

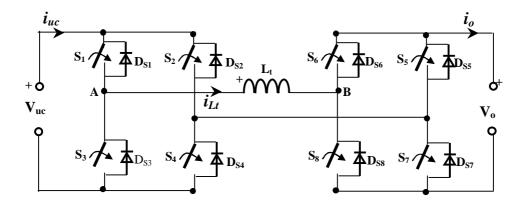

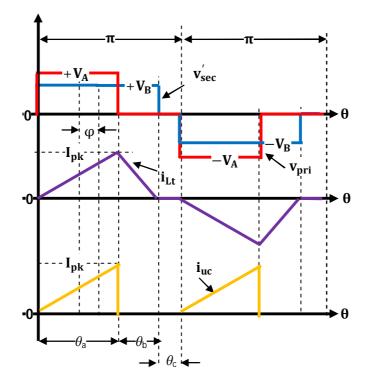

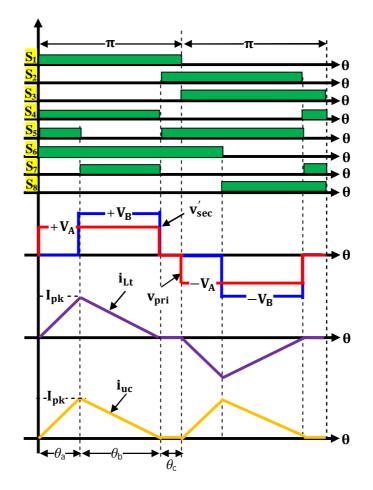

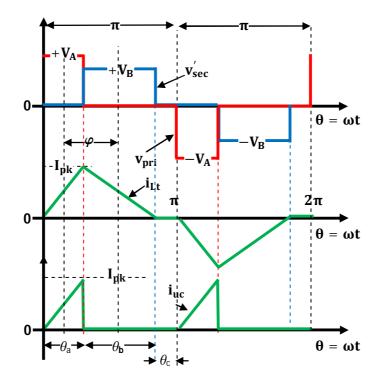

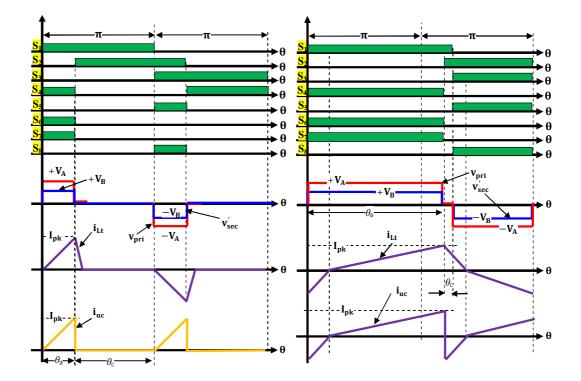

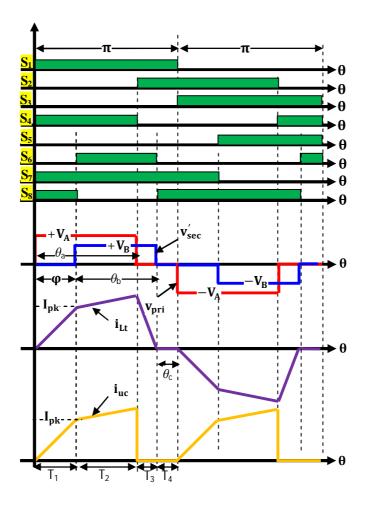

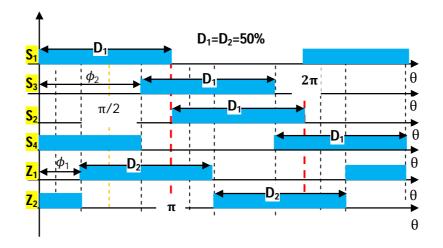

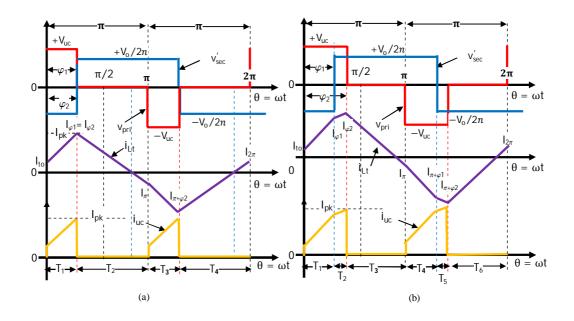

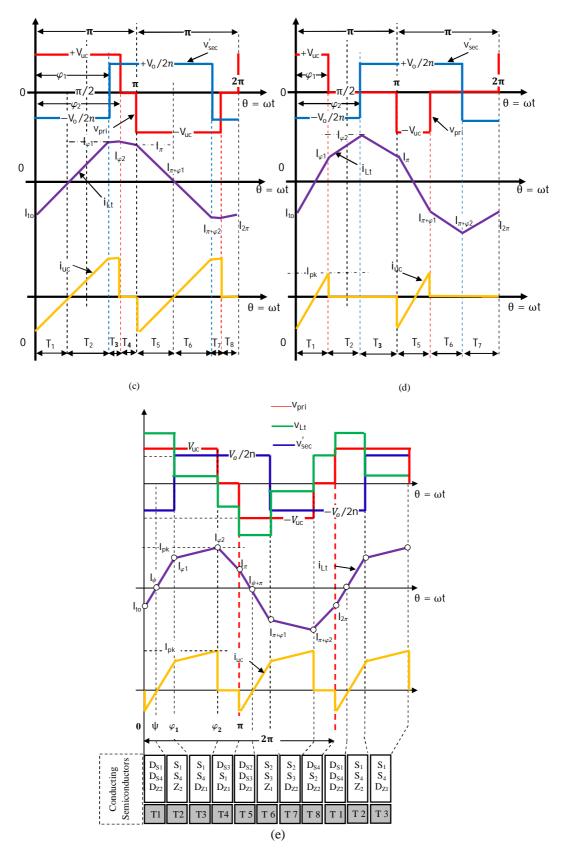

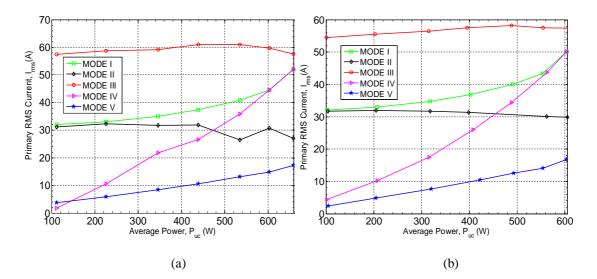

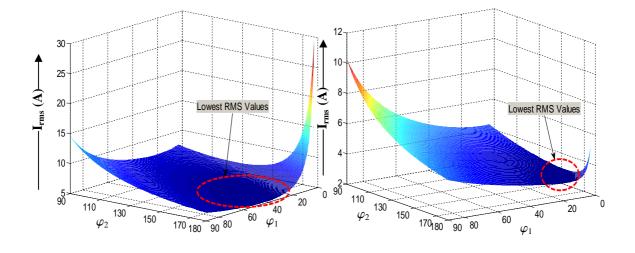

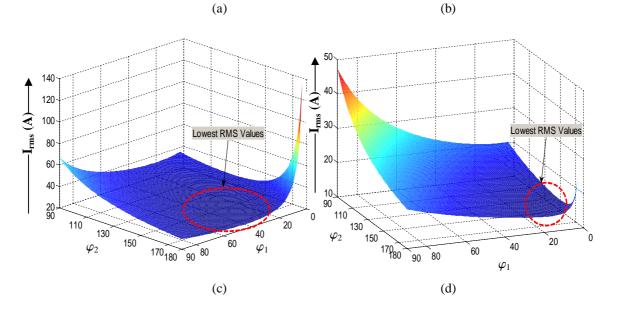

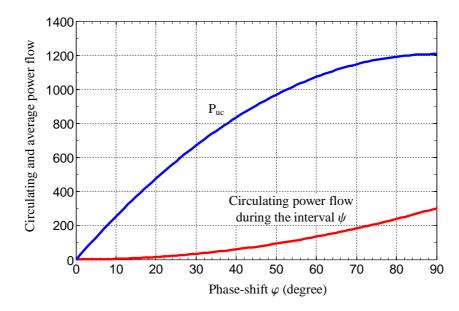

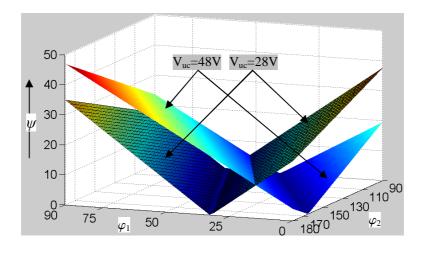

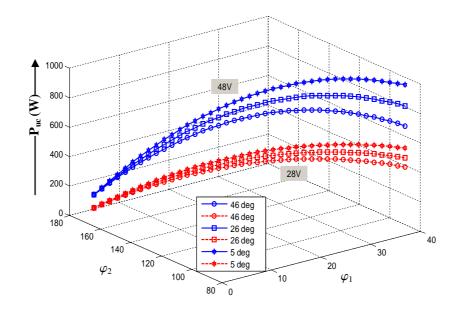

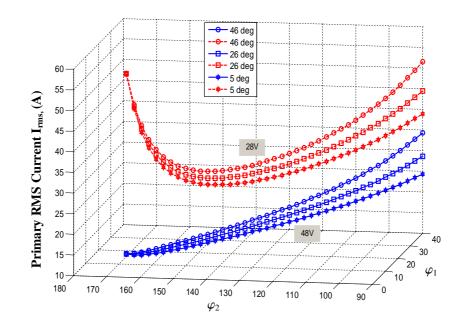

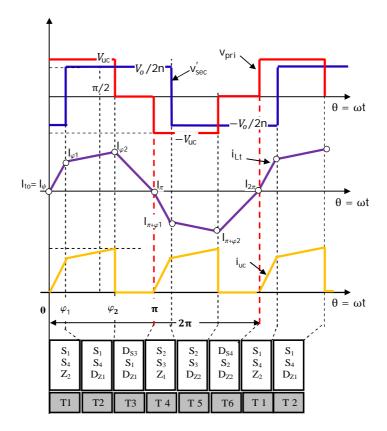

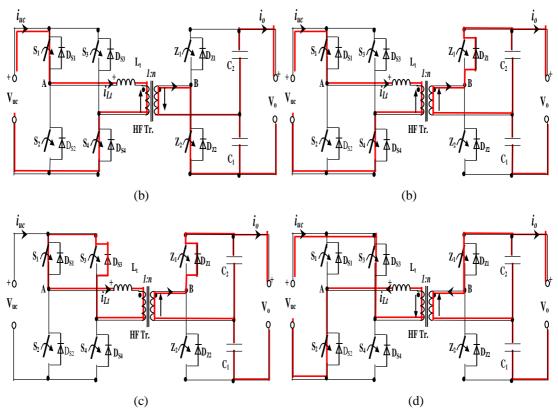

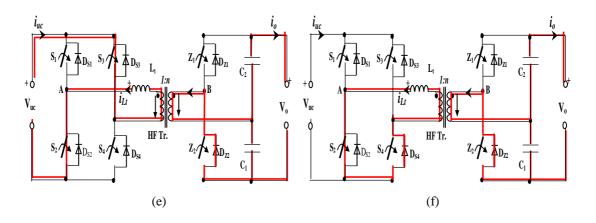

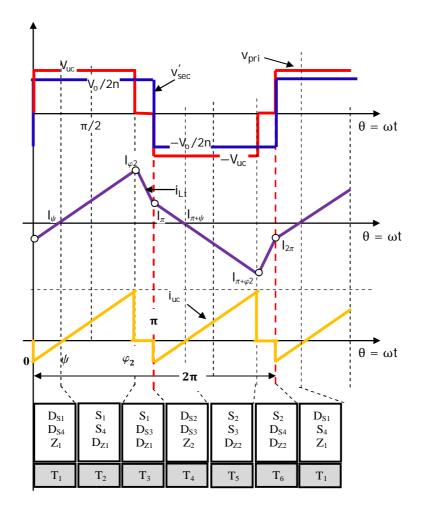

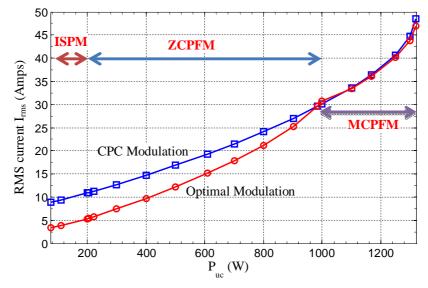

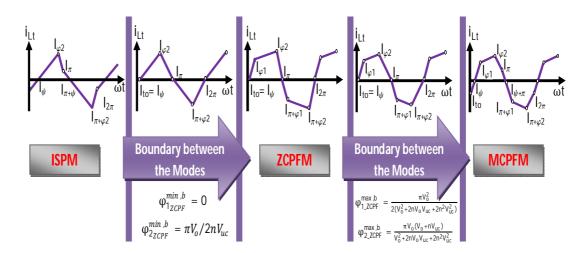

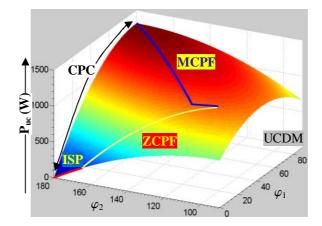

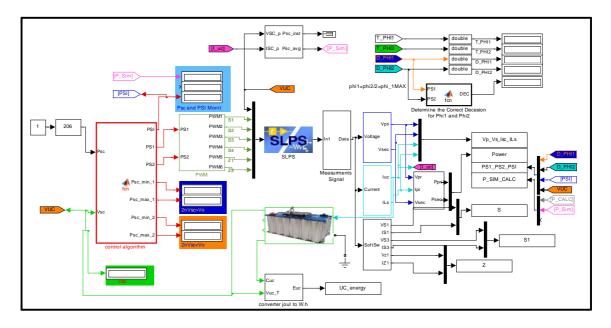

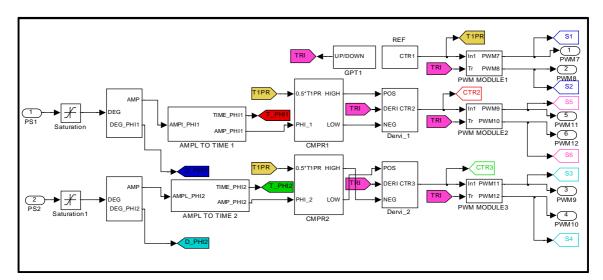

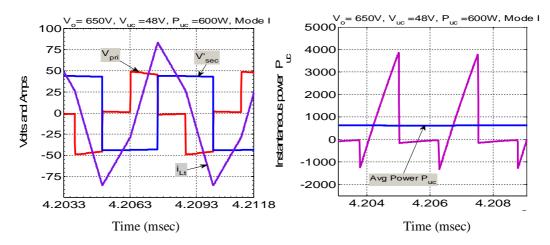

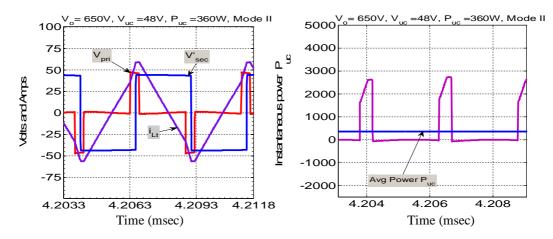

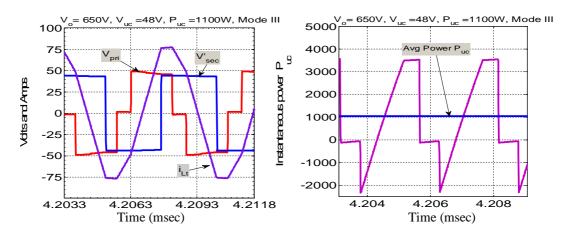

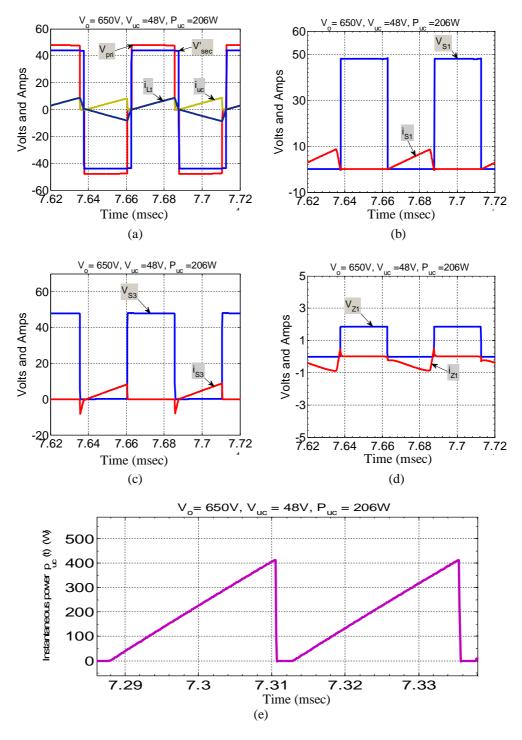

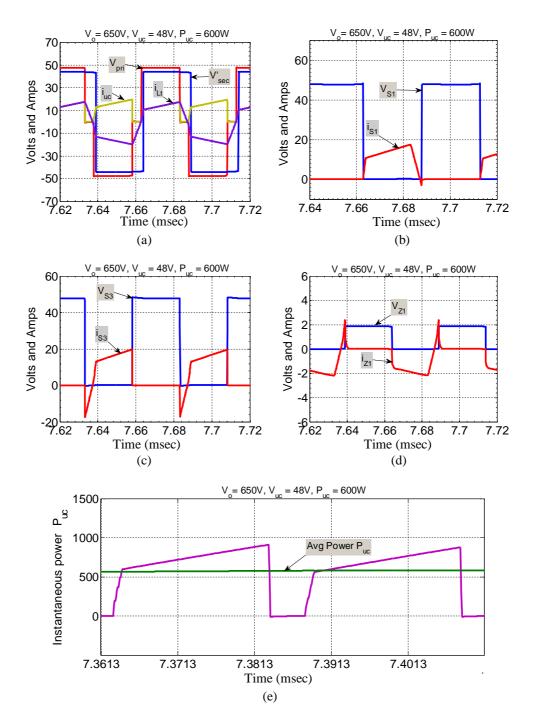

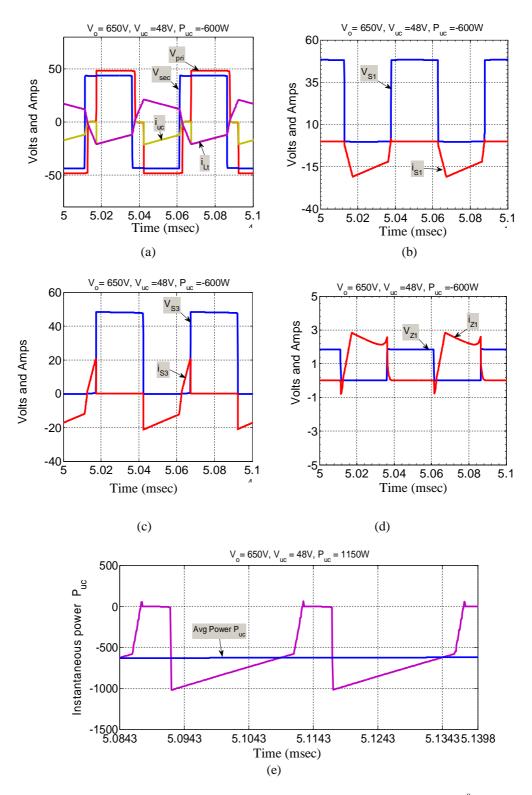

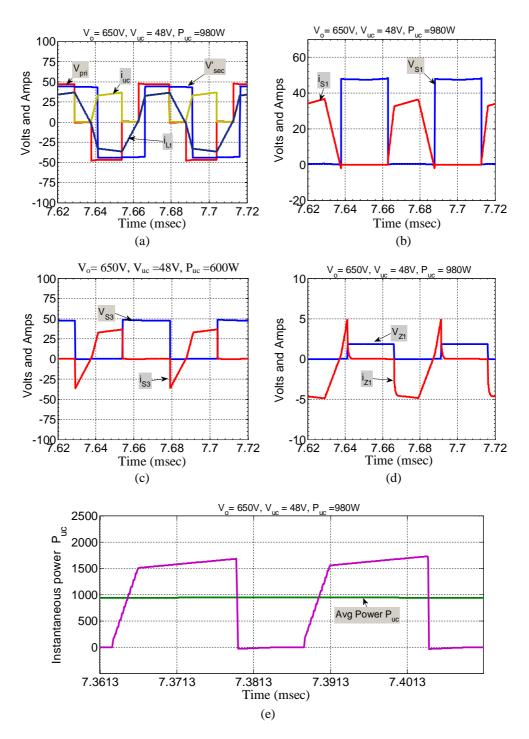

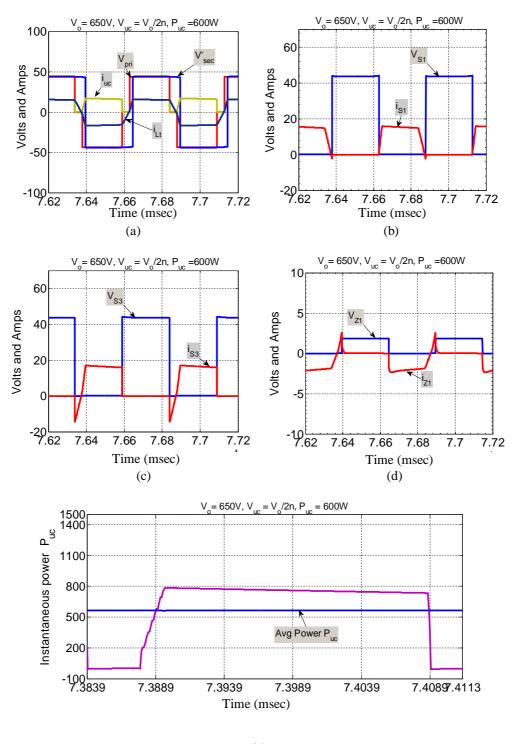

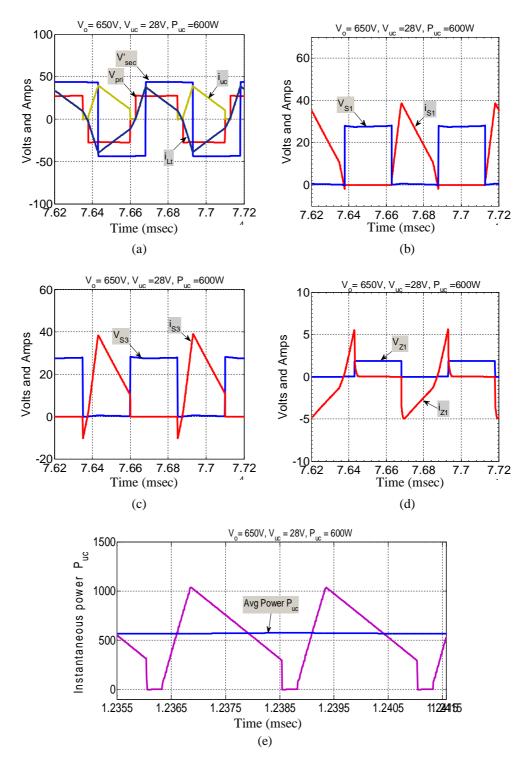

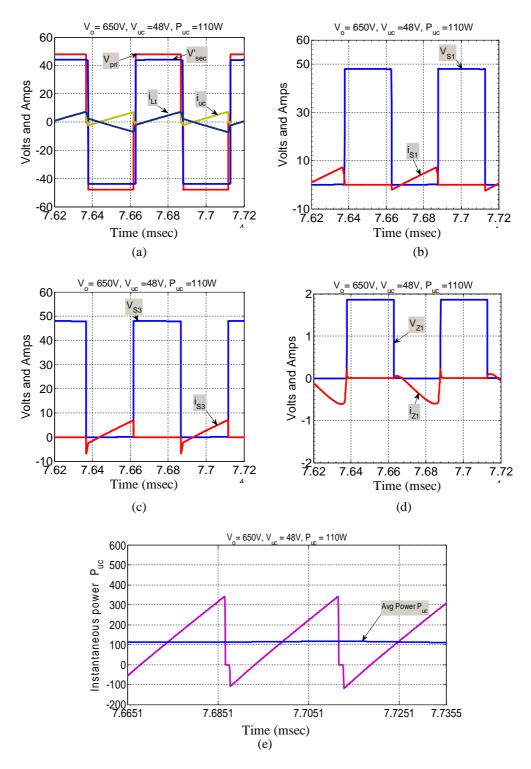

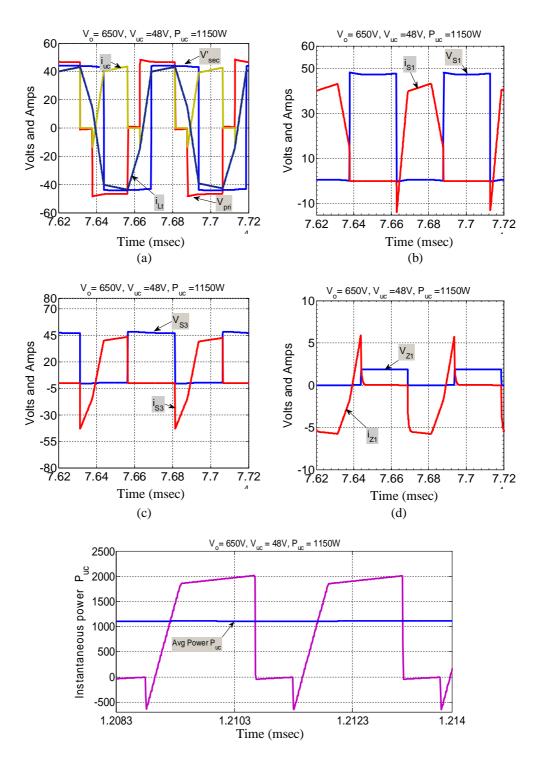

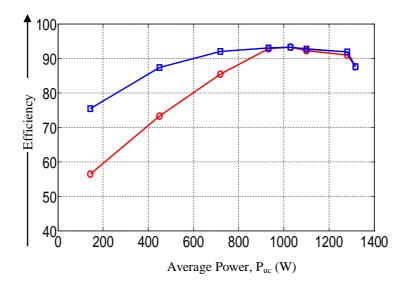

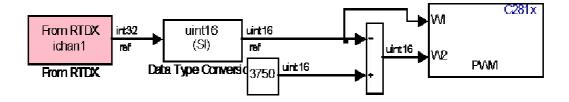

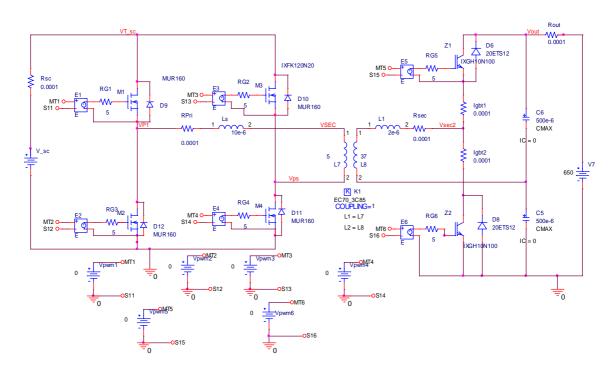

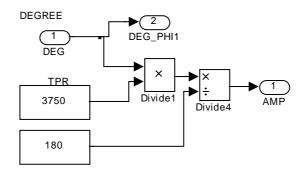

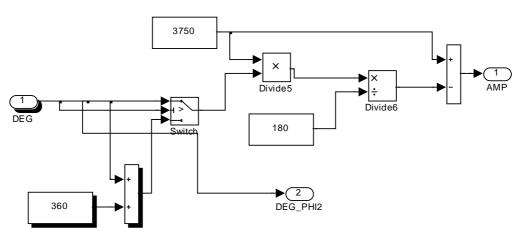

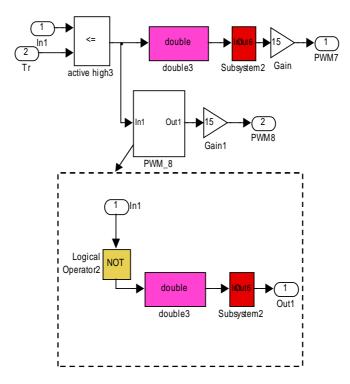

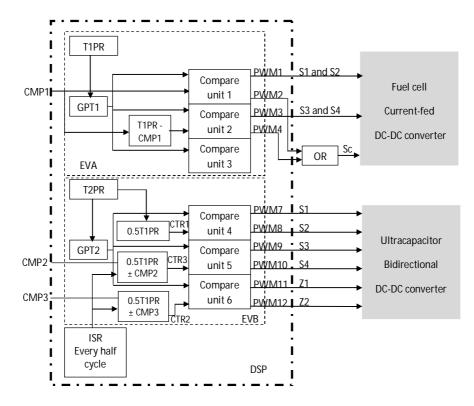

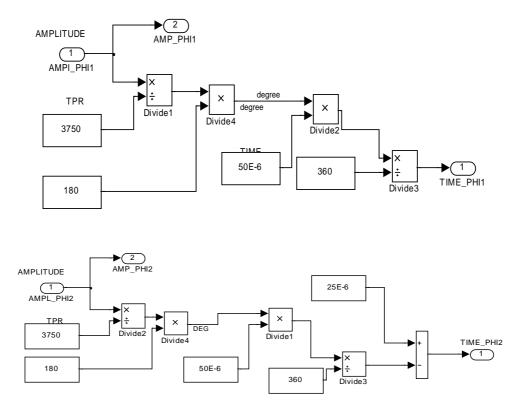

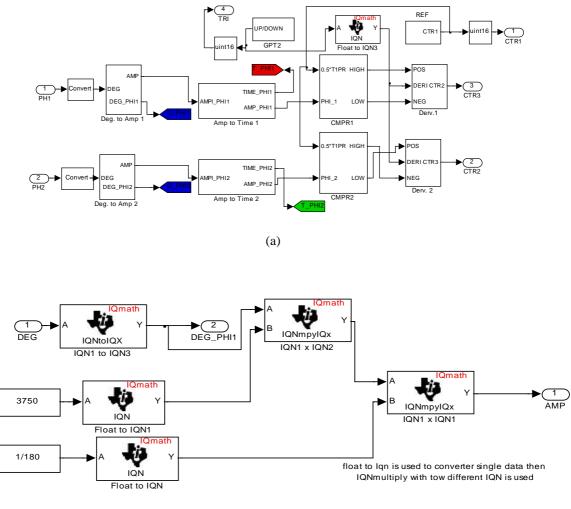

## 2.5.1 Unidirectional DC-DC Converters