## THE DESIGN OF PREDICTABLE MULTI-CORE PROCESSORS

#### WHICH SUPPORT TIME-TRIGGERED SOFTWARE

#### **ARCHITECTURES**

A thesis submitted in fulfilment of the requirements for the degree of

Doctor of Philosophy

By

**Keith Florence Athaide**

Embedded Systems Laboratory

Department of Engineering

University of Leicester

Leicester, United Kingdom

October 2010

# The design of predictable multi-core processors which support time-triggered software architectures

#### Keith F. Athaide

#### ABSTRACT

Safety-critical systems – such as those used in the medical, automotive and aerospace fields – have a crucial dependence on the reliable functioning of one or more embedded processors. In such systems, a co-operative software design methodology can be used to guarantee a high degree of reliability; when coupled with a time-triggered architecture, this methodology can result in robust and predictable systems with a comparatively simple software design, low operating system overhead, easier testability, greater certification support and tight jitter control.

Nevertheless, the use of a co-operative design methodology is not always appropriate, since it may negatively affect system responsiveness and can add to the maintenance costs. Many alternatives have been researched and implemented over the past few decades to address such concerns, albeit by compromising on some of the benefits this architecture provides.

This thesis makes five main contributions to tackle the major obstacles to single-processor time-triggered co-operative designs:

- it proposes and describes the implementation of a novel multi-core processor with two capable software scheduler implementations that allow application software to be designed as for a single-core system;

- it describes the internalisation of these scheduler implementations into hardware which allows application software to use all available computing capacity;

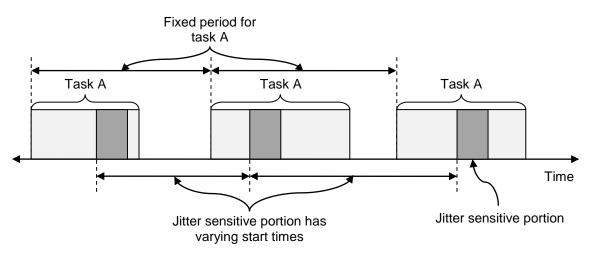

- it describes a hardware technique to eliminate the variations in starting times of application software, thereby increasing the stability of applications;

- it describes the implementation of a hardware technique for sharing input/output resources amongst application software with increased determinism by leveraging the time-triggered nature of the underlying system;

- it describes the implementation of a predictable processor that supports purely co-operative software and is suitable for the secondary cores on a multi-core design (due to its small size).

Overall, the contributions of this thesis both increase system responsiveness and lessen the impact of seemingly innocuous maintenance activities.

#### ACKNOWLEDGEMENTS

First and foremost, I would like to thank the Almighty Triune God for His grace and support mediated through the one Church guided by the See of St. Peter. It is the restlessness of the heart as it seeks God that has led to the pursuit of knowledge in the philosophical, historical, ethical, medical and natural sciences.

I owe my deepest gratitude to my supervisor, Professor Michael J. Pont, for his guidance, patience and encouragement throughout my research; and also for his constant endeavours to be available to his students. I would also like to thank my technical supervisor, Dr. Devaraj Ayavoo, for his support and for all his words of encouragement; and his colleague, Dr. Zemian Hughes for lending an open ear to ludicrous thoughts and for intriguing ideas.

I would like to thank my sponsors for making this research possible: TTE Systems Ltd. for the grant of a studentship, the University of Leicester for the award of an Open Scholarship and the Department of Engineering for the allotment of departmental funding.

Further, I am sincerely grateful to my parish priest, Fr. Leon Pereira O.P., for his help during difficult times and to one of my housemates, Miss Isabel Lim Fong for being a friend. I would also like to thank my other housemates, Dr. Dénes Bisztray, Dr. Cicimol Alexander, Mr. Michael Furniss, Miss Réka Plugor and Miss Dimitrinka Atanasova for their understanding and tolerance of many eccentricities that escalated as time wore on. I extend the same thanks to my colleagues Mr. Syed Aley Imran Rizvi, Dr. Imran Sheikh, Mr. Muhammad Amir, Mr. Musharraf Ahmed Hanif and particularly Miss Farah Lakhani.

Last, but not least, I would like to thank my parents, Mr. Gregorio Taumaturgo Policarpo Francisco Ataide and Mrs. Clara Ditosa Da Cruz é Ataide and my siblings Mrs. Karen Marisa Kaur, Mr. Kevin Tonisavio Athaide and Miss Kate Caroline Athaide for always being there and for their prayers.

There are many others in the parish of Holy Cross Priory Church, in Leicester, in the United Kingdom, on earth, in purgatory and in heaven, too many to name here, to whom I also extend my sincere gratitude. May God bless you all.

# **Table of Contents**

| LIST OF FIGURES                                           | VIII      |

|-----------------------------------------------------------|-----------|

| LIST OF TABLES                                            | XI        |

| LIST OF LISTINGS                                          | XII       |

| LIST OF PUBLICATIONS                                      | XIII      |

| PATENTS                                                   | XIII      |

| CHAPTER 1 INTRODUCTION                                    | 1-1       |

| 1.1 EMBEDDED COMPUTING                                    | 1-3       |

| 1.2 REAL-TIME EMBEDDED SYSTEMS                            | 1-5       |

| 1.3 THE TIME-TRIGGERED CO-OPERATIVE ARCHITECTURE          | 1-6       |

| 1.4 AIMS OF THE THESIS                                    | 1-8       |

| 1.5 Scope                                                 | 1-8       |

| 1.6 Key contributions                                     | 1-9       |

| 1.7 THESIS OVERVIEW                                       | 1-11      |

| 1.8 CONCLUSIONS                                           | 1-12      |

| CHAPTER 2 SOFTWARE ARCHITECTURE OF REAL-TIME SYSTEM SCHED | JLERS 2-1 |

| 2.1 INTRODUCTION                                          | 2-1       |

| 2.2 ENVIRONMENTAL INTERACTION                             | 2-2       |

| 2.3 CLASSIFICATIONS                                       | 2-4       |

| 2.4 HARDWARE MODEL                                        | 2-6       |

| 2.5 SOFTWARE DEVELOPMENT MODEL                            | 2-7       |

| 2.6 The task model                                        | 2-9       |

| 2.6.1 HARMONIC DEPENDENCIES BETWEEN PERIODS               | 2-12      |

| 2.6.2 OTHER TYPES OF TASKS                                | 2-13      |

| 2.6.3 LATENCY                                             | 2-13      |

| 2.6.4 JITTER                                              | 2-13      |

| 2.6.4.1 EXECUTION JITTER                                  | 2-14      |

| 2.6.4.2 COMPLETION JITTER                                 | 2-15      |

| 2.6.4.3 FINISHING JITTER                                  | 2-16      |

| 2.6.4.4 RELEASE JITTER                                    | 2-16      |

| 2.7 SHARED RESOURCE MANAGEMENT                            | 2-17      |

| 2.7.1 BLOCKING TECHNIQUES                                 |           |

| 2.7.2 Non-blocking techniques                               | 2-20           |

|-------------------------------------------------------------|----------------|

| 2.7.3 Multi-processor                                       | 2-22           |

| 2.7.4 PERIPHERAL MANAGEMENT                                 | 2-23           |

| 2.8 REAL-TIME TASK SCHEDULING                               | 2-24           |

| 2.8.1 THE SCHEDULING ALGORITHM                              | 2-25           |

| 2.8.1.1 RUN-TIME COMPLEXITY                                 | 2-27           |

| 2.8.2 The trigger architecture                              | 2-27           |

| 2.8.3 THE EXECUTION ARCHITECTURE                            | 2-29           |

| 2.8.4 MULTI-PROCESSOR SCHEDULING                            | 2-30           |

| 2.8.5 A PART OF THE SYSTEM                                  | 2-31           |

| 2.9 THE COMPLEXITY OF DESIGN                                | 2-32           |

| 2.10 CONCLUSIONS                                            | 2-33           |

| CHAPTER 3 THE TIME-TRIGGERED CO-OPERATIVE ARCHITECTURE      | 3-1            |

| 3.1 INTRODUCTION                                            | 3-1            |

| 3.2 ARCHITECTURE DESIGN                                     | 3-1            |

| 3.2.1 THE TTCA MODEL                                        | 3-3            |

| 3.2.2 TIMING EVENT GENERATOR                                | 3-5            |

| 3.2.3 TASK DESIGN                                           | 3-5            |

| 3.2.4 PRIORITY ASSIGNMENTS                                  | 3-6            |

| 3.3 FEASIBILITY                                             | 3-6            |

| 3.4 PROCESSOR UTILISATION                                   | 3-7            |

| 3.5 Fragility                                               | 3-7            |

| 3.6 EXISTING IMPLEMENTATIONS                                |                |

| 3.6.1 THE CYCLIC EXECUTIVE ARCHITECTURE                     | 3-8            |

| 3.6.2 TABLE-FREE MULTI-RATE EXECUTIVE (TTC)                 | 3-11           |

| 3.6.3 TIME-EVENT QUEUE                                      | 3-13           |

| 3.6.4 MULTIPLE TIMER INTERRUPTS (TTC-SHD)                   | 3-13           |

| 3.6.5 HARDWARE MULTI-RATE EXECUTIVE (HW-TTC)                | 3-16           |

| 3.6.6 OTHER IMPLEMENTATIONS                                 | 3-19           |

| 3.7 CONCLUSIONS                                             | 3-20           |

| CHAPTER 4 PROBLEMS WITH THE TIME-TRIGGERED CO-OPERATIVE ARC | CHITECTURE 4-1 |

| 4.1 INTRODUCTION                                            | 4-1            |

| 4.2 MAINTAINABILITY                                         | 4-2            |

| 4.3 The long-task problem                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| 4.3.1 IMPROVED HARDWARE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          |

| 4.3.2 IMPROVED ALGORITHMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-5                      |

| 4.3.3 BREAKING UP LONG-TASKS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-5                      |

| 4.3.4 PRE-EMPTIVE DESIGNS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-6                      |

| 4.3.5 INCREASED CONCURRENCY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4-8                      |

| 4.4 TASK JITTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-8                      |

| 4.4.1 IMPROVED ALGORITHMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-10                     |

| 4.4.2 Task properties                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4-11                     |

| 4.4.3 UTILISING SPARE COMPUTATIONAL CAPACITY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 4-12                     |

| 4.4.3.1 SINGLE PATH PROGRAMMING                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-12                     |

| 4.4.3.2 CODE BALANCING WITH DELAYS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 4-12                     |

| 4.4.4 JITTER SENSITIVE CODE INSIDE A TASK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 4-14                     |

| 4.5 Non-harmonic task-sets                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 4-15                     |

| 4.6 CONCLUSIONS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 4-16                     |

| CHAPTER 5 INCREASING THE CONCURRENCY IN SINGLE-PROCESSOR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| 5.1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-1                      |

| 5.1 INTRODUCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5-1<br>5-2               |

| 5.1 INTRODUCTION<br>5.2 DESIGN CHOICES<br>5.2.1 INCREASING CONCURRENCY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5-1<br>5-2<br>5-2        |

| <ul> <li>5.1 INTRODUCTION</li> <li>5.2 DESIGN CHOICES</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5-1<br>5-2<br>5-2<br>5-4 |

| <ul> <li>5.1 INTRODUCTION</li> <li>5.2 DESIGN CHOICES</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          |

| <ul> <li>5.1 INTRODUCTION</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

| <ul> <li>5.1 INTRODUCTION</li> <li>5.2 DESIGN CHOICES</li> <li>5.2.1 INCREASING CONCURRENCY</li> <li>5.2.2 INTER CORE COMMUNICATION</li> <li>5.2.3 CONSTRAINTS</li> <li>5.3 SELECTING A SOFT MULTI-CORE PROCESSOR</li> <li>5.3.1 EXISTING SOFT MULTI-CORES</li> <li>5.3.2 SOFT-CORES WITH NO MULTI-CORE PLATFORMS</li> <li>5.3.3 THE PH CORE</li> <li>5.3.3.1 MICROCONTROLLER BLOCK DIAGRAM</li> <li>5.3.3.2 A SINGLE INTERRUPT</li> <li>5.3.3.3 GUARANTEED INSTRUCTION EXECUTION TIMES</li> <li>5.3.3.4 GUARANTEED MEMORY LATENCY</li> </ul>                                                                                                      |                          |

| <ul> <li>5.1 INTRODUCTION</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

| <ul> <li>5.1 INTRODUCTION</li> <li>5.2 DESIGN CHOICES</li> <li>5.2.1 INCREASING CONCURRENCY</li> <li>5.2.2 INTER CORE COMMUNICATION</li> <li>5.2.3 CONSTRAINTS</li> <li>5.3 SELECTING A SOFT MULTI-CORE PROCESSOR</li> <li>5.3.1 EXISTING SOFT MULTI-CORES</li> <li>5.3.2 SOFT-CORES WITH NO MULTI-CORE PLATFORMS</li> <li>5.3.3 THE PH CORE</li> <li>5.3.3.1 MICROCONTROLLER BLOCK DIAGRAM</li> <li>5.3.3.2 A SINGLE INTERRUPT</li> <li>5.3.3.3 GUARANTEED INSTRUCTION EXECUTION TIMES</li> <li>5.3.3.4 GUARANTEED MEMORY LATENCY</li> <li>5.3.3.5 CONSTANT INTERRUPT OVERHEAD (PH-MT)</li> <li>5.4 A PROCESSOR WITH MULTIPLE PH CORES</li> </ul> |                          |

| <ul> <li>5.1 INTRODUCTION</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          |

|     | 5.5.1 Overview                                                   | 5-17  |

|-----|------------------------------------------------------------------|-------|

|     | 5.5.2 CREATING THE DESCRIPTIONS                                  | 5-20  |

|     | 5.5.3 Writing                                                    | 5-20  |

|     | 5.5.4 Reading                                                    | 5-21  |

|     | 5.5.5 Switching between buffers                                  | 5-21  |

| 5.  | 6 THE SCHEDULER DESIGN                                           | 5-25  |

|     | 5.6.1 OVERVIEW                                                   | 5-25  |

|     | 5.6.2 PRECEDENCE CONSTRAINTS                                     | 5-26  |

|     | 5.6.3 DETERMINISTIC INITIALISATION SEQUENCE                      | 5-27  |

|     | 5.6.4 THE MULTIPLE SCHEDULE BUILDERS IMPLEMENTATION (TTC-MC-MSB) | 5-29  |

|     | 5.6.5 THE SINGLE SCHEDULE BUILDER IMPLEMENTATION (TTC-MC-1SB)    | 5-30  |

| 5.  | 7 EVALUATION                                                     | 5-33  |

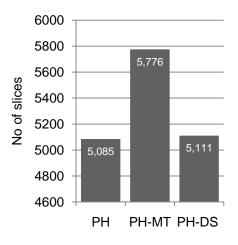

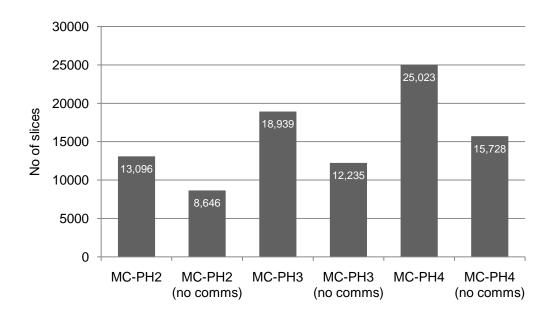

|     | 5.7.1 HARDWARE UTILISED                                          | 5-34  |

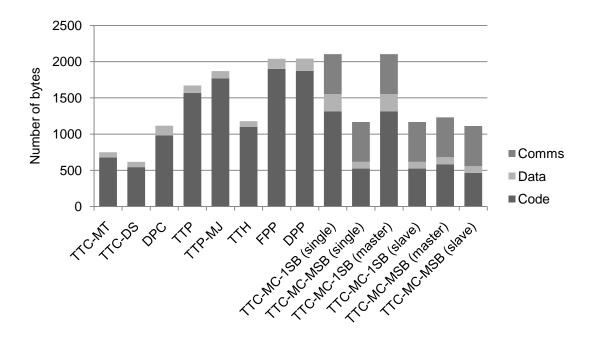

|     | 5.7.1.1 Results                                                  | 5-34  |

|     | 5.7.2 INTER CORE COMMUNICATION                                   | 5-36  |

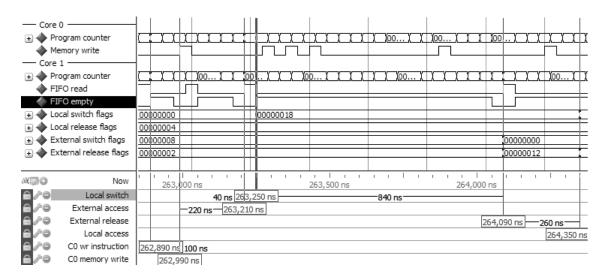

|     | 5.7.2.1 HARDWARE RESULTS                                         | 5-37  |

|     | 5.7.2.2 SIMULATION RESULTS                                       | 5-39  |

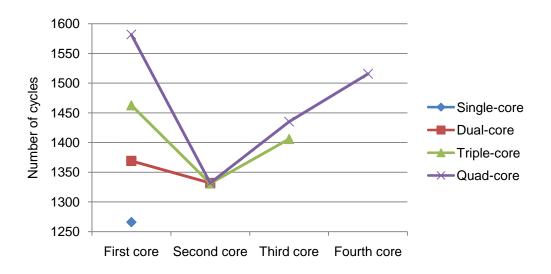

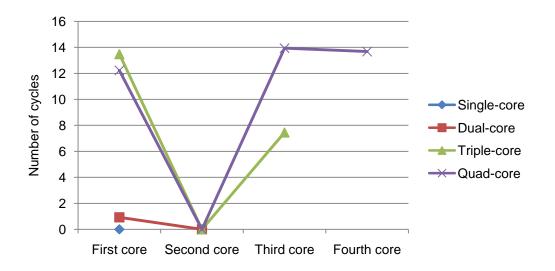

|     | 5.7.3 INITIALISATION                                             | 5-40  |

|     | 5.7.3.1 Results                                                  | 5-41  |

| 5.  | 8 CONCLUSIONS                                                    | 5-43  |

| Сна | PTER 6 CASE STUDY: F-16 FLIGHT SYSTEM                            | . 6-1 |

| 6.  | 1 INTRODUCTION                                                   | . 6-1 |

| 6.  | 2 TECHNICAL DETAILS                                              | . 6-1 |

| 6.  | 3 Setup                                                          | . 6-4 |

| 6.  | 4 MEASURED TASK TIMING                                           | . 6-7 |

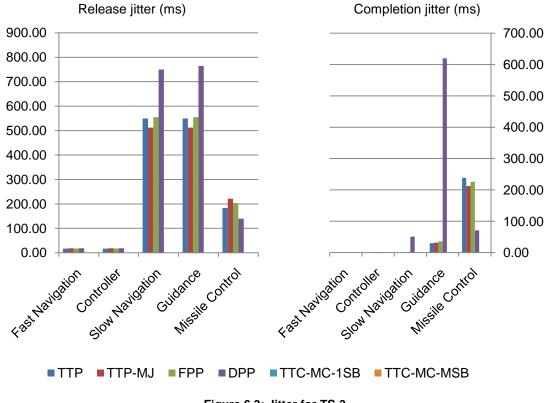

| 6.  | 5 RELEASE AND COMPLETION JITTER                                  | . 6-7 |

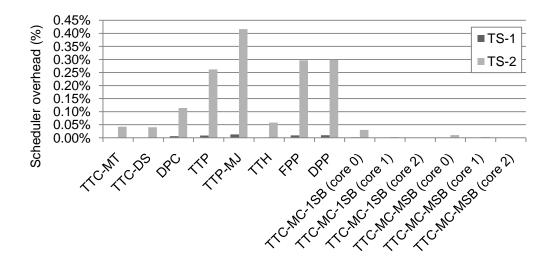

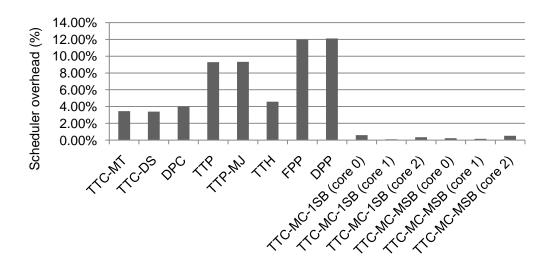

| 6.  | 6 OVERHEADS                                                      | 6-10  |

| 6.  | 7 DISCUSSION                                                     | 6-13  |

| 6.  | 8 CONCLUSIONS                                                    | 6-15  |

| Сна | PTER 7 A TTCA MULTI-CORE HARDWARE IMPLEMENTATION                 | . 7-1 |

| 7.  | 1 INTRODUCTION                                                   | . 7-1 |

| 7.  | 2 Related work                                                   | . 7-2 |

| 7.  | 3 HW-TTC SUPPORT FOR PRECISE EXCEPTIONS                          | . 7-4 |

| 7.4 A HARDWARE TTCA IMPLEMENTATION WITH ZERO OVERHEADS     | 7-5  |

|------------------------------------------------------------|------|

| 7.5 THE HARDWARE MULTIPLE SCHEDULE BUILDERS IMPLEMENTATION | 7-8  |

| 7.6 THE HARDWARE SINGLE SCHEDULE BUILDER IMPLEMENTATION    | 7-9  |

| 7.7 A PURE HARDWARE SANDWICH DELAY MECHANISM (-HSD)        | 7-10 |

| 7.8 EVALUATION                                             | 7-12 |

| 7.8.1 RELEASE AND COMPLETION JITTER                        | 7-12 |

| 7.8.2 OVERHEADS                                            | 7-15 |

| 7.8.3 SIMULATION                                           | 7-18 |

| 7.9 CONCLUSIONS                                            |      |

| CHAPTER 8 CASE STUDY: THE BR715 ENGINE CONTROLLER          | 8-1  |

| 8.1 INTRODUCTION                                           | 8-1  |

| 8.2 TECHNICAL DETAILS                                      | 8-2  |

| 8.3 Previous work                                          | 8-2  |

| 8.4 A STATIC SCHEDULE CREATION ALGORITHM                   | 8-3  |

| 8.4.1 SCHEDULE CREATION                                    |      |

| 8.4.2 TASK PARTITIONING                                    | 8-5  |

| 8.5 EVALUATION PLATFORM                                    | 8-6  |

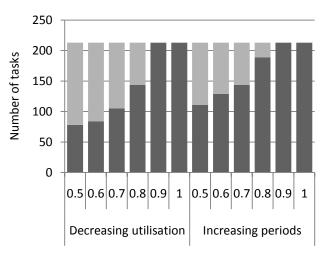

| 8.6 TASK DISTRIBUTION                                      | 8-6  |

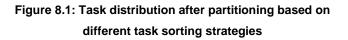

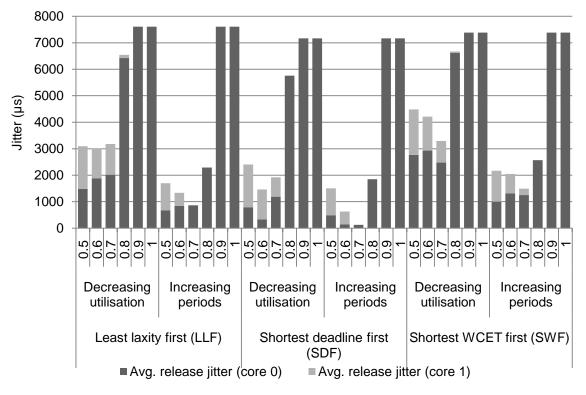

| 8.7 Release jitter                                         |      |

| 8.8 TICK INTERVAL                                          | 8-10 |

| 8.9 COMPUTATION TIME                                       | 8-10 |

| 8.10 CONCLUSION                                            | 8-12 |

| CHAPTER 9 NON-BLOCKING TRANSPARENT RESOURCE SHARING        |      |

| 9.1 INTRODUCTION                                           |      |

| 9.2 INPUT/OUTPUT RESOURCES                                 |      |

| 9.3 DESIGN CONSTRAINTS                                     |      |

| 9.3.1 Non-blocking scheme                                  |      |

| 9.3.2 Low jitter                                           |      |

| 9.4 Related work                                           |      |

| 9.4.1 The gateway scheme                                   |      |

| 9.4.2 PARTITIONING RESOURCES                               |      |

| 9.4.3 TIME-DIVISION MULTIPLE ACCESS                        |      |

| 9.4.4 Other approaches                                     |      |

| 9.5 GLOBAL AND PROXY PERIPHERALS                               |          |

|----------------------------------------------------------------|----------|

| 9.5.1 A TIME-TRIGGERED APPROACH                                |          |

| 9.5.2 TRANSACTION CAPABLE                                      | 9-10     |

| 9.5.2.1 MARKING THE CRITICAL SECTIONS                          |          |

| 9.5.2.2 TIMED ACCESS                                           |          |

| 9.5.2.3 INTELLIGENT PERIPHERALS                                |          |

| 9.6 GLOBALISING THE GPIO PERIPHERAL                            |          |

| 9.7 GLOBALISING THE ADC PERIPHERAL                             | 9-13     |

| 9.8 EVALUATION                                                 | 9-15     |

| 9.9 OPERATIONAL JITTER                                         |          |

| 9.10 HARDWARE UTILISATION                                      |          |

| 9.11 CONCLUSIONS                                               |          |

| CHAPTER 10 DISCUSSION AND CONCLUSIONS                          | 10-1     |

| 10.1 INTRODUCTION                                              | 10-1     |

| 10.2 Multi-core TTCA IMPLEMENTATIONS                           | 10-2     |

| 10.3 HARDWARE MULTI-CORE TTCA IMPLEMENTATIONS                  |          |

| 10.4 An I/O RESOURCE SHARING SCHEME                            | 10-5     |

| 10.5 A SIMPLER, BUT PREDICTABLE PROCESSOR                      | 10-6     |

| 10.6 Multi-core schedule creation algorithm                    | 10-6     |

| 10.7 LIMITATIONS                                               | 10-7     |

| 10.8 NOVELTY CONTRIBUTIONS                                     | 10-8     |

| 10.9 RECOMMENDATIONS FOR FUTURE WORK                           | 10-9     |

| APPENDIX A GLOSSARY                                            | A-1      |

| A.1 ABBREVIATIONS                                              | A-1      |

| A.2 DEFINITIONS USED BY THE TASK MODEL                         | A-6      |

| A.3 UNITS                                                      | A-8      |

| A.4 NOTATIONS                                                  | A-8      |

| APPENDIX B THE THREE BUFFER SINGLE-WRITER, SINGLE-READER MECH. | ANISMB-1 |

| B.1 INTRODUCTION                                               | B-1      |

| B.2 THE DESIGN OF THE MECHANISM                                | B-2      |

| B.3 CONCLUSIONS                                                | B-4      |

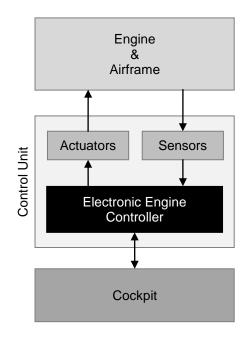

| APPENDIX C THE BR715 ENGINE CONTROLLER                         | C-1      |

| C.1 PURPOSE OF THE ELECTRONIC ENGINE CONTROLLER SYSTEM         | C-1      |

| E | BIBLIOGRAPHY              | Вів-1 |

|---|---------------------------|-------|

|   | C.4 CONCLUSIONS           | C-4   |

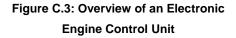

|   | C.3 TRANSACTION DEADLINES | C-3   |

|   | C.2 TASK DETAILS          | C-2   |

# List of Figures

| FIGURE 1.1: THE TRANSFORMATION WILL REPLACE A SINGLE-CORE PROCESSOR WITH A        |

|-----------------------------------------------------------------------------------|

| MULTI-CORE ONE THAT PRESERVES THE $I/O$ INTERFACE WITH OTHER HARDWARE AND         |

| THE SOFTWARE API                                                                  |

| FIGURE 2.1: EFFECT OF TIME ON THE QUALITY OF A REAL-TIME COMPUTATION              |

| (AUDSLEY ET AL. 1990)                                                             |

| FIGURE 2.2: LATENCY AND JITTER OF A RESPONSE                                      |

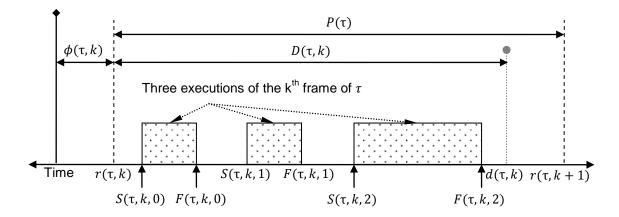

| FIGURE 2.3: AN EXAMPLE $kth$ frame of a task $	au$ which has three executions2-10 |

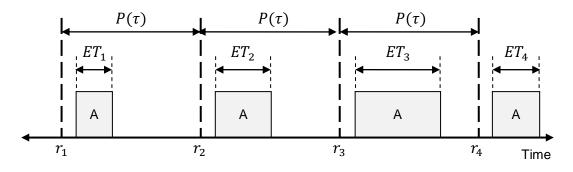

| FIGURE 2.4: EXECUTION JITTER IN PERIODIC TASKS                                    |

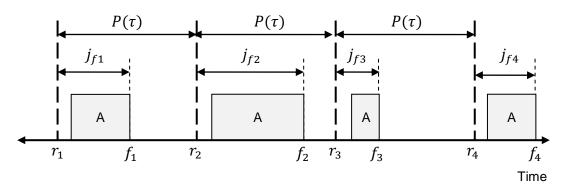

| FIGURE 2.5: FINISHING JITTER IN PERIODIC TASKS                                    |

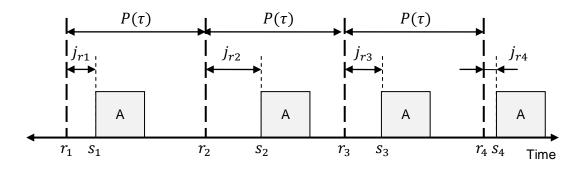

| FIGURE 2.6: RELEASE JITTER IN PERIODIC TASKS                                      |

| FIGURE 2.7: A FEW OF THE PROBLEMS WITH RESOURCE SHARING: (A) RESOURCE             |

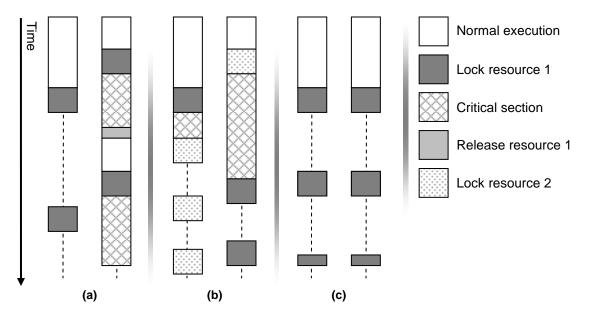

| STARVATION; (B) DEADLOCK; (C) LIVELOCK                                            |

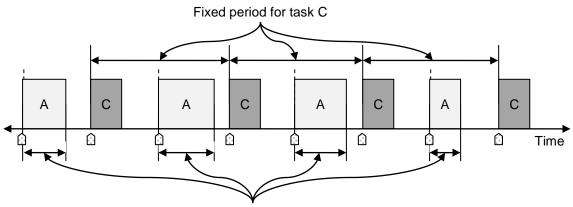

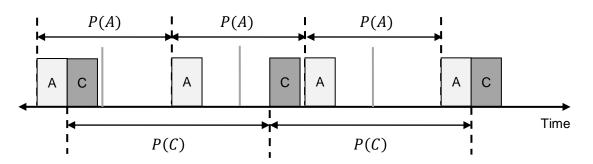

| FIGURE 3.1: OPERATION OF TTCA ACCORDING TO THE SCHEDULE                           |

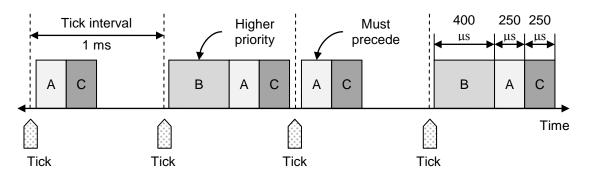

| FIGURE 3.2: OVERHEADS IN A TTCA IMPLEMENTATION                                    |

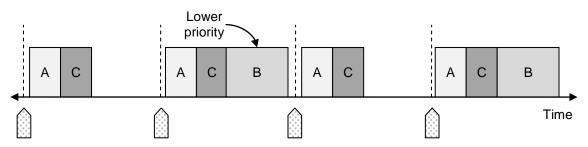

| FIGURE 3.3: EFFECT OF LOWERING THE PRIORITY OF TASK B                             |

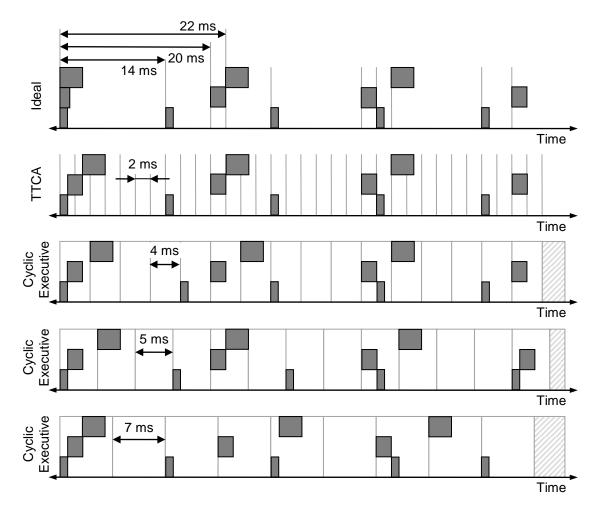

| FIGURE 3.4: EXECUTION OF TASKS WITH PERIODS 14 MS, 20 MS, 22 MS, FROM TOP TO      |

| BOTTOM: THE IDEAL CASE; TTCA WITH A TICK OF 2 MS; CYCLIC EXECUTIVES WITH TICK     |

| INTERVALS OF 4 MS, 5 MS, 7 MS                                                     |

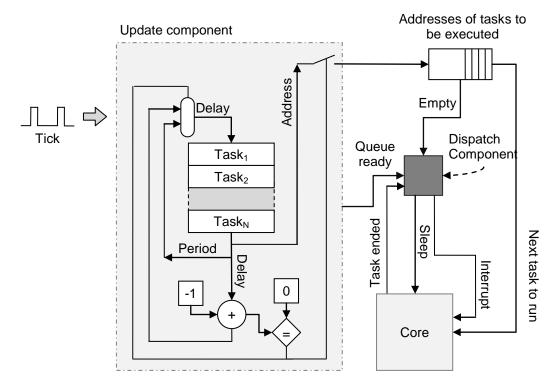

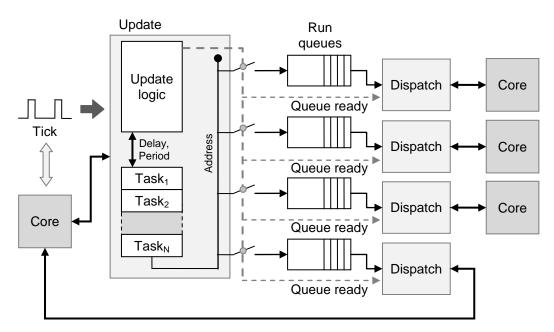

| FIGURE 3.5: FUNCTIONAL OVERVIEW OF THE HARDWARE MULTI-RATE EXECUTIVE 3-17         |

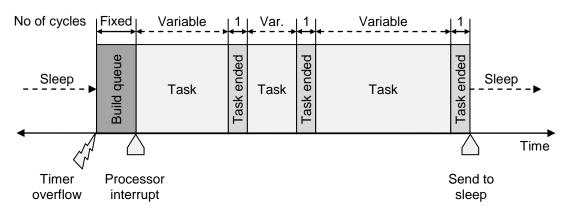

| FIGURE 3.6: TIMELINE VIEW OF THE HW-TTC OPERATION                                 |

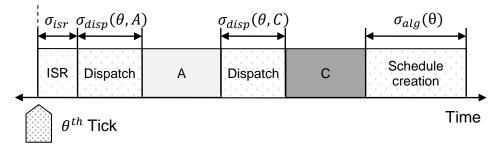

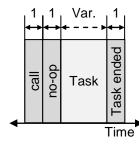

| FIGURE 3.7: SCHEDULING OVERHEAD ON ONE TASK                                       |

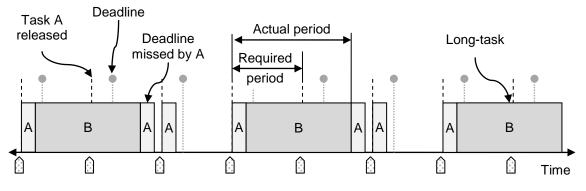

| FIGURE 4.1: LONG-TASK CAUSING DEADLINES TO BE MISSED                              |

| FIGURE 4.2: HANDLING A LONG-TASK WITH THE TTH ARCHITECTURE                        |

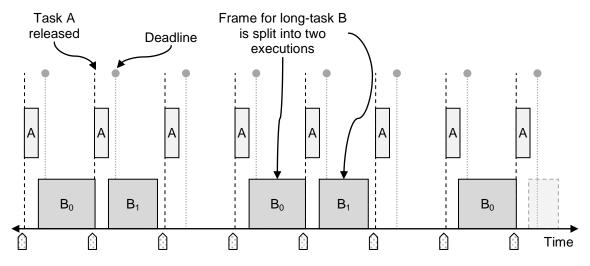

| FIGURE 4.3: RELEASE JITTER CAUSED BY EXECUTION JITTER IN A PRECEDING TASK. 4-9    |

| FIGURE 4.4: HIGH EXECUTION JITTER MAY CAUSE HIGH RELEASE JITTER IN A PORTION      |

| OF A TASK WHICH OTHERWISE HAS LOW RELEASE JITTER                                  |

| FIGURE 4.5: EFFECT OF PHASES AND AN INCREASE IN TICK RATES ON RELEASE JITTER      |

| CAUSED BY EXECUTION JITTER IN A PREVIOUS TASK                                     |

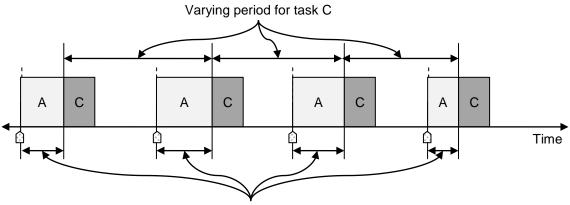

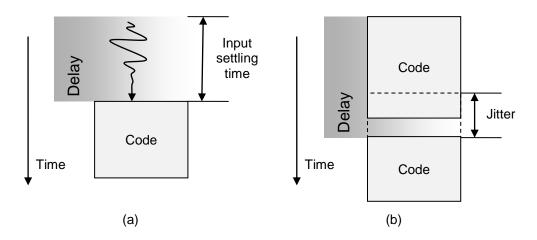

| FIGURE 4.6: USING DELAYS TO PLACE GUARANTEES ON THE EXECUTION TIME 4-13           |

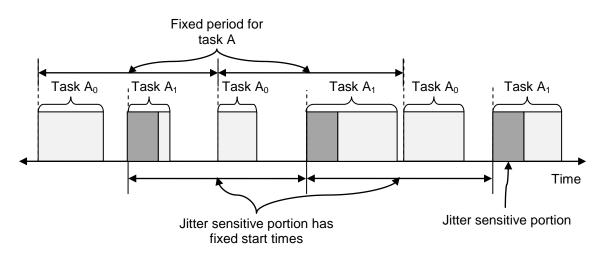

| FIGURE 4.7: CREATING NEW TASKS TO HANDLE A JITTER-SENSITIVE PORTION INSIDE A      |

| TASK                                                                              |

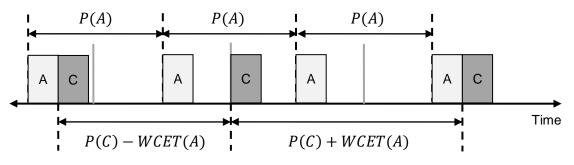

| FIGURE 4.8: RELEASE JITTER CAUSED BY NON-HARMONIC PERIODS                         |

| FIGURE 4.9: ATTEMPTING TO REDUCE RELEASE JITTER CAUSED BY NON-HARMONIC            |

| PERIODS BY INSERTING DELAYS                                                       |

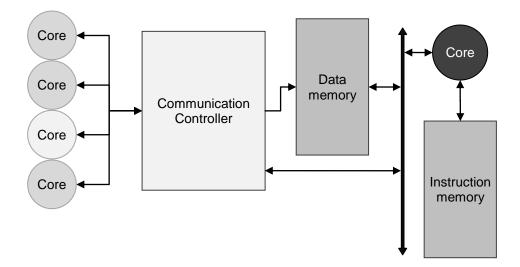

| FIGURE 5.1: A GENERIC SINGLE PROCESSOR DESIGN                                     |

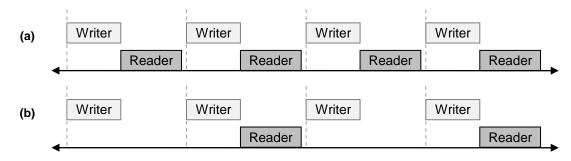

| FIGURE 5.2: READER AND WRITER TASKS RUNNING AT DIFFERENT RATES                    |

| FIGURE 5.3: POSSIBLE OVERLAPS BETWEEN A WRITER AND A READER (KOPETZ ET AL.        |

| 1993)                                                                             |

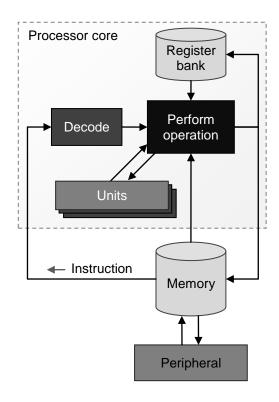

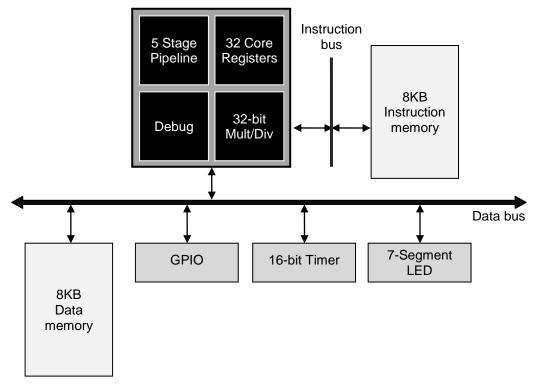

| FIGURE 5.4: PH PROCESSOR IMPLEMENTATION (HUGHES 2009)                             |

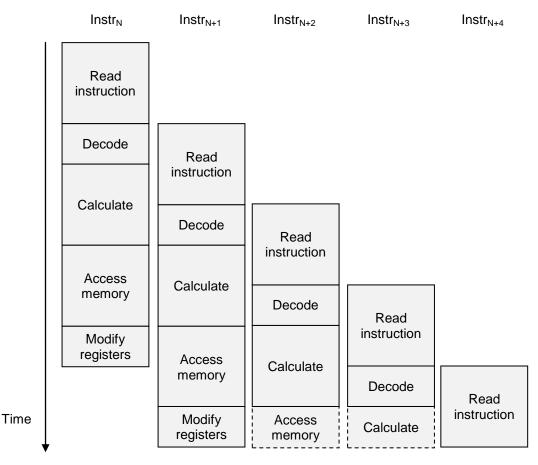

| FIGURE 5.5: FIVE STAGE PIPELINE IN THE PH CORE                                    |

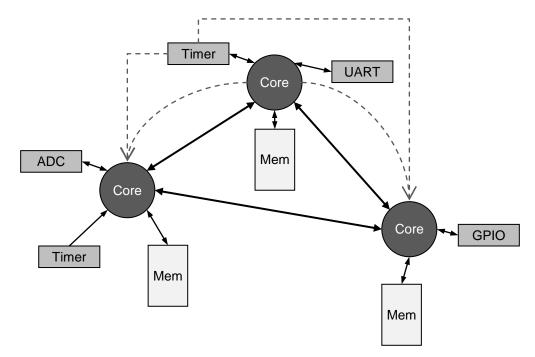

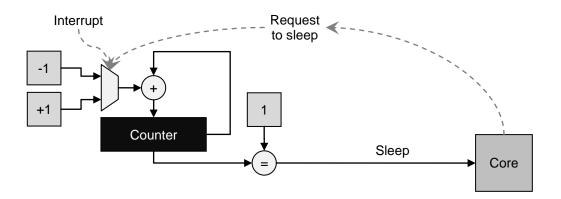

| FIGURE 5.6: HARDWARE ORGANISATION                                                           | 5 |

|---------------------------------------------------------------------------------------------|---|

| FIGURE 5.7: THE PH-DS MECHANISM                                                             | 6 |

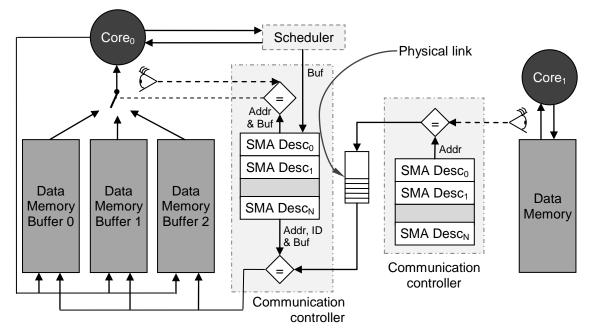

| FIGURE 5.8: OVERVIEW OF THE COMMUNICATION HARDWARE                                          |   |

| FIGURE 5.9: AN OVERVIEW OF COMMUNICATION BETWEEN TWO CORES                                  | 0 |

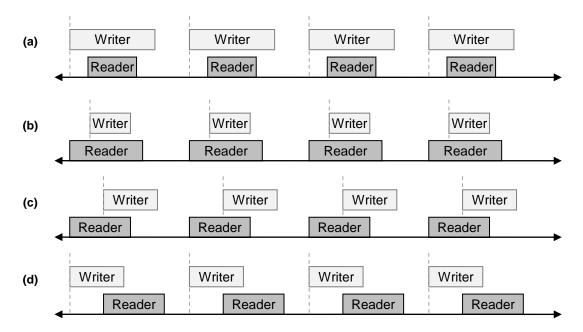

| FIGURE 5.10: STATES OF A BUFFER                                                             | 2 |

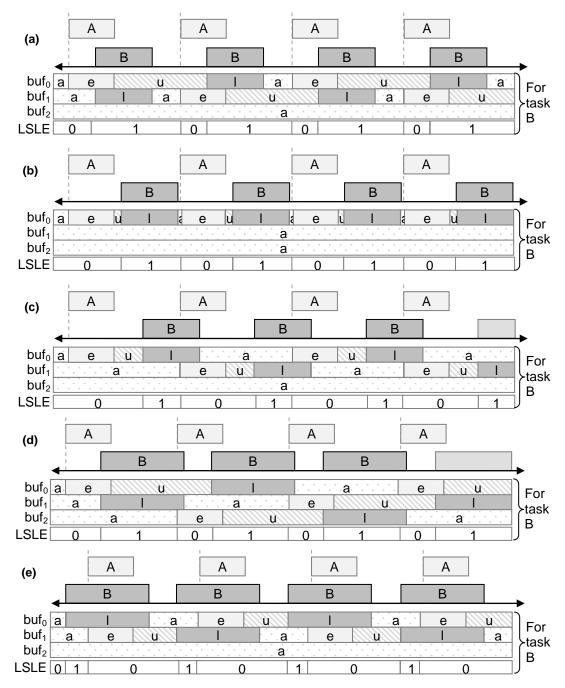

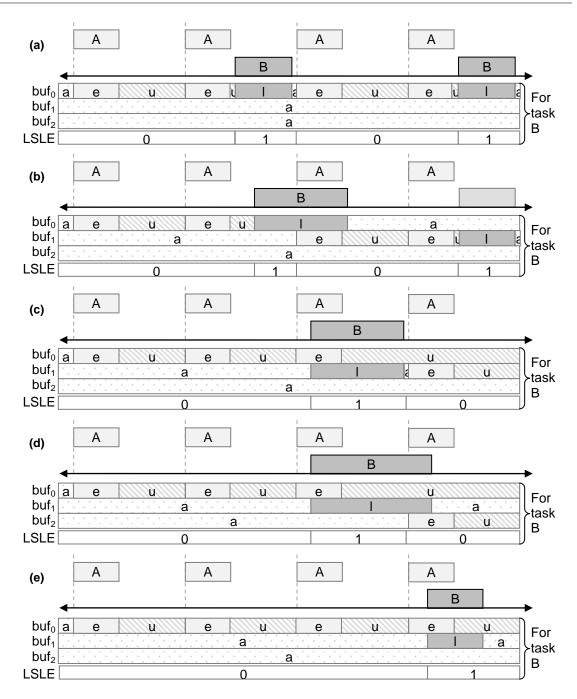

| FIGURE 5.11: BUFFER SWITCHES FROM THE VIEW OF TASK B WHEN IT OVERLAPS WITH                  | Η |

| A TASK A RUNNING AT THE SAME RATE WITH A COMBINED UTILISATION LESS THAN ON                  |   |

| FIGURE 5.12: BUFFER SWITCHES FROM THE VIEW OF TASK B WHEN IT OVERLAPS WITH                  | Η |

| A TASK A RUNNING AT TWICE THE RATE                                                          | 5 |

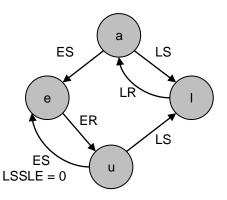

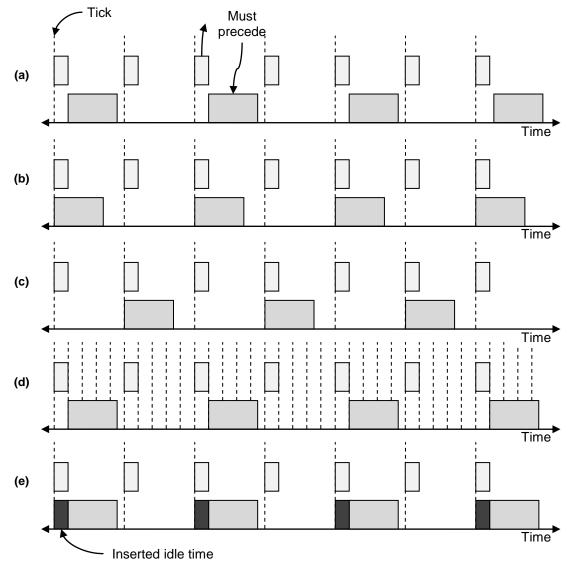

| FIGURE 5.13: (A) USING TASK ORDER TO ENFORCE PRECEDENCE CONSTRAINTS IN A                    | A |

| SEQUENTIAL SYSTEM, (B) HAS NO EFFECT IN CONCURRENT EXECUTION WHICH MUST B                   |   |

| HANDLED (C) BY CHANGING PHASES, (D) BY INCREASING THE TICK INTERVAL OR (E) B                |   |

| INSERTING IDLE TIME                                                                         |   |

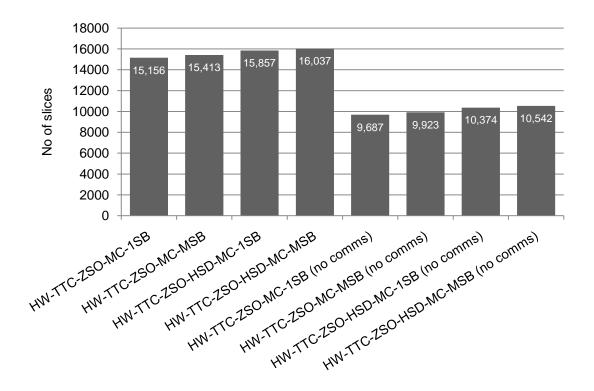

| FIGURE 5.15: HARDWARE UTILISATION ON REMOVING THE COMMUNICATION                             |   |

| MECHANISM FROM MC-PHN IMPLEMENTATIONS                                                       |   |

| FIGURE 5.14: HARDWARE UTILISATION ON CHANGING THE CORE TYPE                                 |   |

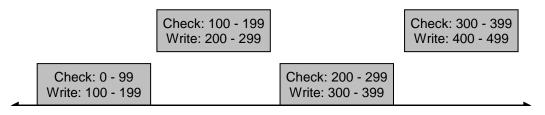

| FIGURE 5.16: TASK FUNCTIONALITY FOR INTER CORE COMMUNICATION EVALUATION . 5                 | - |

| 37                                                                                          | ~ |

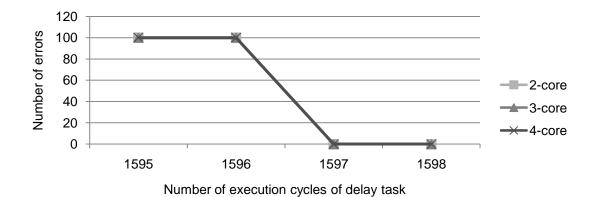

| FIGURE 5.17: NUMBER OF ERRORS ENCOUNTERED BY $\tau 1$                                       |   |

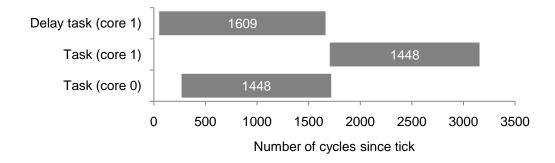

| FIGURE 5.18: SNAPSHOT OF TASK EXECUTION ON A DUAL-CORE WITH NO ERRORS (N                    |   |

| = 399, 0 NOPs, $\omega$ = 1599 CYCLES)                                                      |   |

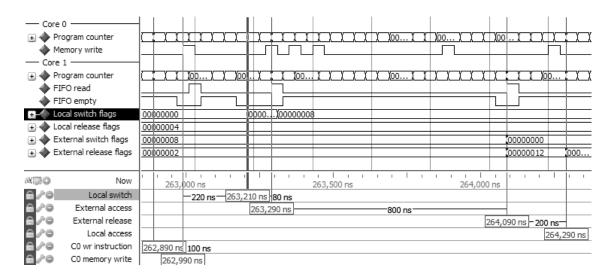

| FIGURE 5.19: SIMULATION OF BUFFER SWITCHES WITH ERRORS AT $\omega = 1596$ CYCLES            |   |

|                                                                                             |   |

| Figure 5.20: Simulation of buffer switches just after errors stop at $\omega$ = 1597 cycles |   |

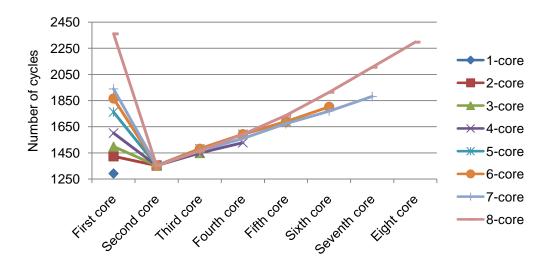

| FIGURE 5.21: AVERAGE NUMBER OF CYCLES TAKEN FOR A CORE TO INITIALISE ON ONE                 |   |

| TO FOUR-CORE DEVICES                                                                        |   |

| FIGURE 5.22: STANDARD DEVIATION IN INITIALISATION TIMES ON ONE- TO FOUR-COR                 |   |

| DEVICES                                                                                     |   |

| FIGURE 5.23: NUMBER OF CYCLES TAKEN FOR A CORE TO INITIALISE ON SIMULATEI                   |   |

| ONE- TO EIGHT-CORE DEVICES                                                                  |   |

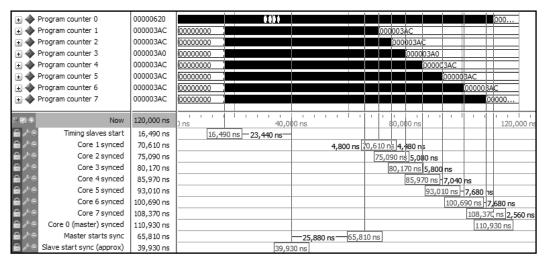

| FIGURE 5.24: SIMULATION OF THE INITIALISATION SEQUENCE FOR 8-CORES                          |   |

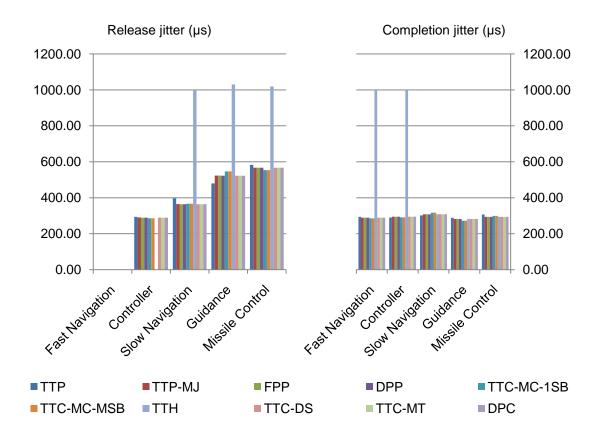

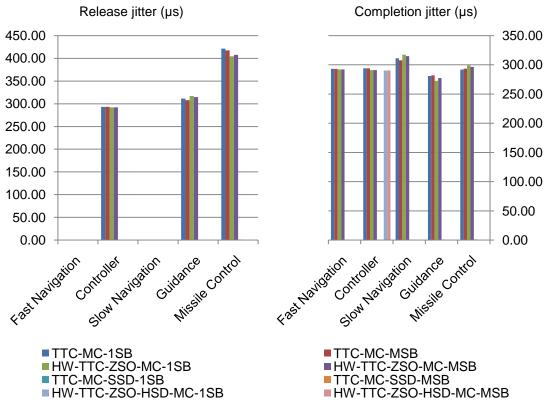

| FIGURE 6.1: JITTER FOR TS-1                                                                 |   |

| FIGURE 6.2: JITTER FOR TS-2                                                                 | 9 |

| FIGURE 6.3: JITTER FOR TS-3                                                                 | 0 |

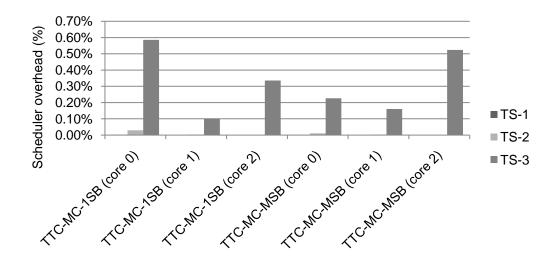

| FIGURE 6.4: SOFTWARE OVERHEAD OF THE SCHEDULER IMPLEMENTATIONS                              | 1 |

| FIGURE 6.5: RUN-TIME OVERHEAD OF THE SCHEDULER IMPLEMENTATIONS RELATIVE TO                  | С |

| THE TICK INTERVAL FOR TS-1 AND TS-2                                                         | 2 |

| FIGURE 6.6: RUN-TIME OVERHEAD OF THE SCHEDULER IMPLEMENTATIONS RELATIVE TO                  | С |

| THE TICK INTERVAL FOR TS-1                                                                  | 2 |

| FIGURE 6.7: RUN-TIME OVERHEAD OF THE MULTI-CORE SCHEDULER IMPLEMENTATION                    | S |

| RELATIVE TO THE TICK INTERVAL                                                               | 3 |

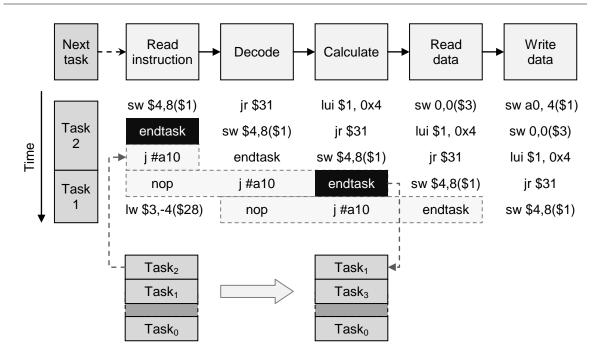

| FIGURE 7.1: THE EFFECT OF THE ENDTASK INSTRUCTION ON THE RUN QUEUES AND   |

|---------------------------------------------------------------------------|

| INSTRUCTION EXECUTION                                                     |

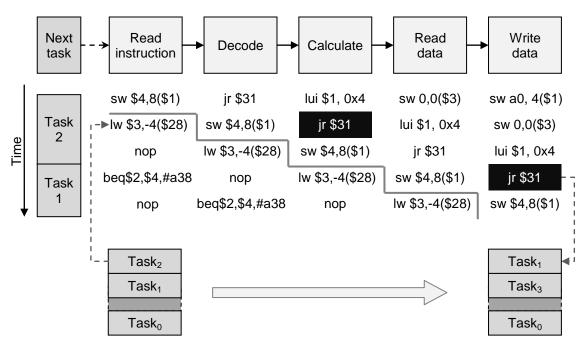

| FIGURE 7.2: THE EFFECT OF OVERLOADING JR WITH THE WORK OF ENDTASK         |

| FIGURE 7.3: FUNCTIONAL OVERVIEW OF THE HARDWARE MULTI-CORE MULTIPLE       |

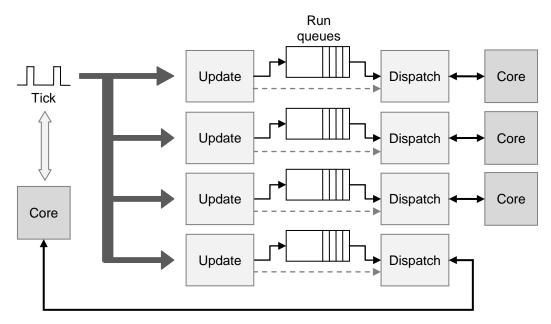

| SCHEDULE BUILDER SCHEDULER                                                |

| FIGURE 7.4: FUNCTIONAL OVERVIEW OF THE HARDWARE MULTI-CORE SINGLE         |

| SCHEDULE BUILDER SCHEDULER                                                |

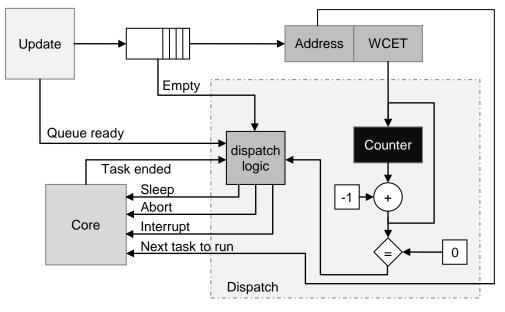

| FIGURE 7.5: CHANGES MADE TO THE DISPATCH COMPONENT TO SUPPORT SANDWICH    |

| DELAYS                                                                    |

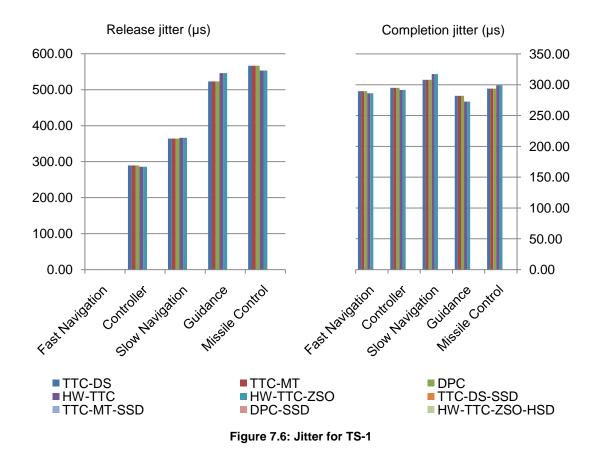

| FIGURE 7.6: JITTER FOR TS-1                                               |

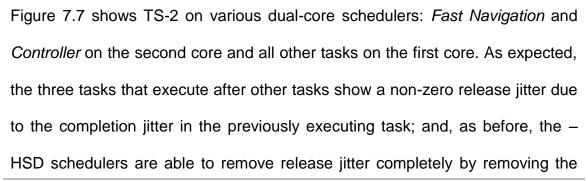

| FIGURE 7.7: JITTER FOR TS-2                                               |

| FIGURE 7.8: JITTER FOR TS-3                                               |

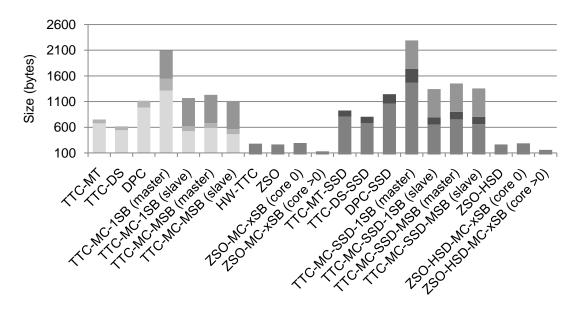

| FIGURE 7.9: SOFTWARE OVERHEAD OF THE SCHEDULER IMPLEMENTATIONS            |

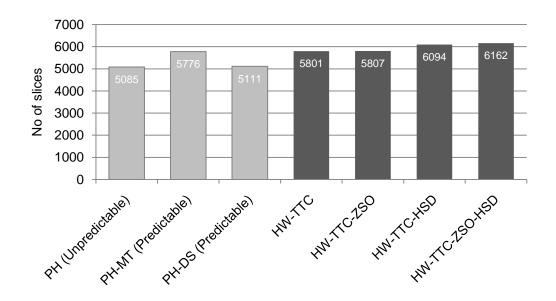

| FIGURE 7.10: HARDWARE UTILISATION WHEN USING A HARDWARE SCHEDULER WITH    |

| AND WITHOUT THE OVERHEAD AND JITTER REDUCTION MECHANISMS                  |

| FIGURE 7.11: HARDWARE UTILISATION WHEN USING A MULTI-CORE HARDWARE        |

| SCHEDULER WITH AND WITHOUT THE JITTER REDUCTION MECHANISM AND INTER-CORE  |

| COMMUNICATION                                                             |

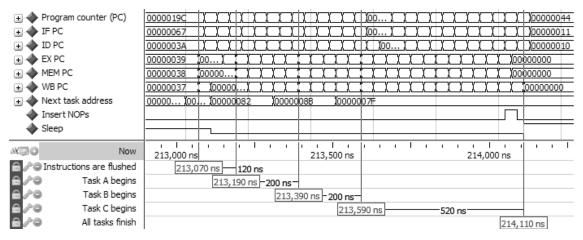

| FIGURE 7.12: SAMPLE EXECUTION OF THREE TASKS UNDER HW-TTC                 |

| FIGURE 7.13: SAMPLE EXECUTION UNDER HW-TTC-ZSO                            |

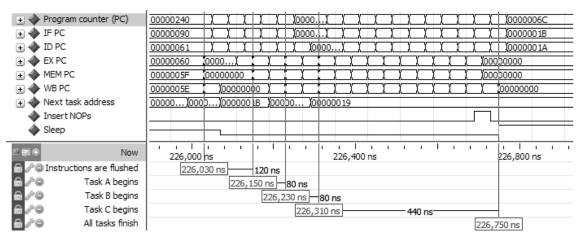

| FIGURE 7.14: SCHEDULE CREATION FOR A DUAL-CORE HW-TTC-ZSO-MC-1SB. 7-20    |

| FIGURE 8.1: TASK DISTRIBUTION AFTER PARTITIONING BASED ON DIFFERENT TASK  |

| SORTING STRATEGIES                                                        |

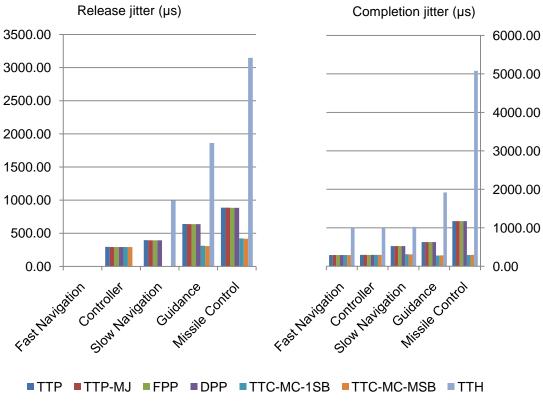

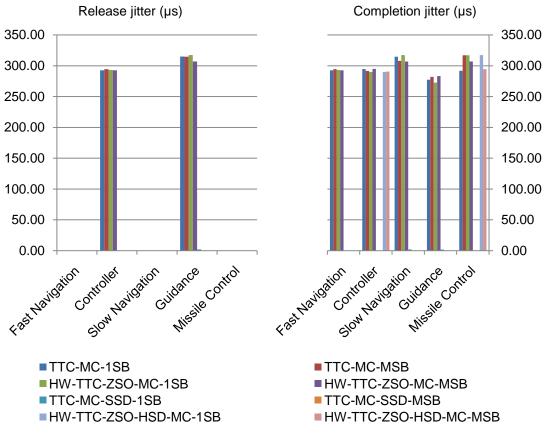

| FIGURE 8.2: RELEASE JITTER WHEN USING TTSA1 WITH DIFFERENT STRATEGIES 8-8 |

| FIGURE 8.3: RELEASE JITTER WHEN USING TTSA1-JR UNDER DIFFERENT STRATEGIES |

|                                                                           |

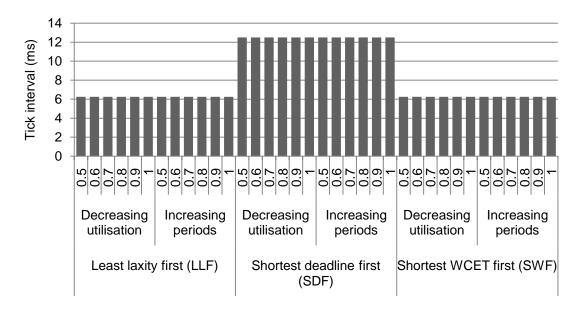

| FIGURE 8.4: TASK INTERVALS UNDER THE DIFFERENT STRATEGIES                 |

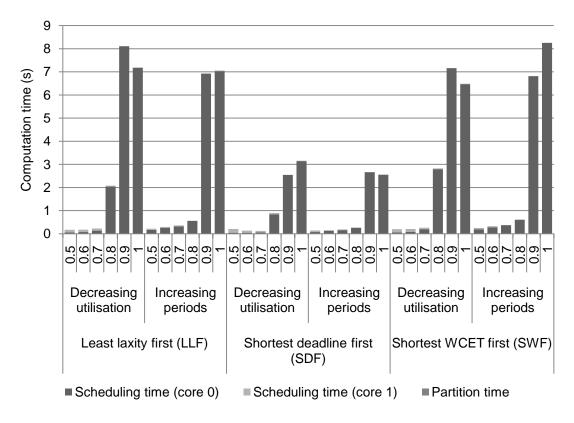

| FIGURE 8.5: TIME TAKEN TO COMPUTE THE SCHEDULES WITH TTSA1                |

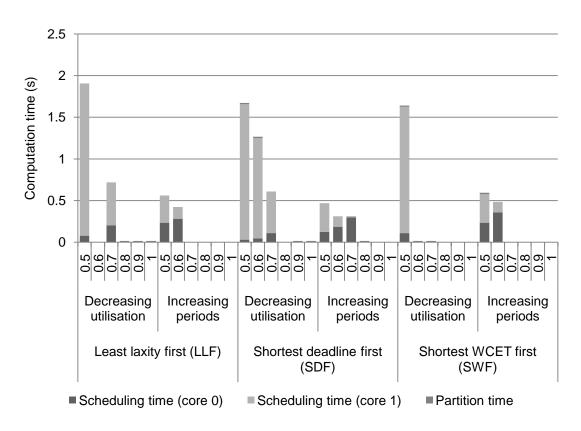

| FIGURE 8.6: TIME TAKEN TO COMPUTE THE SCHEDULES WITH TTSA1-JR             |

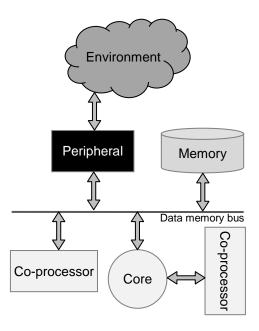

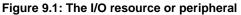

| FIGURE 9.1: THE I/O RESOURCE OR PERIPHERAL                                |

| FIGURE 9.2: GLOBAL PERIPHERALS AND PROXIES TO ALLOW RESOURCE SHARING 9-7  |

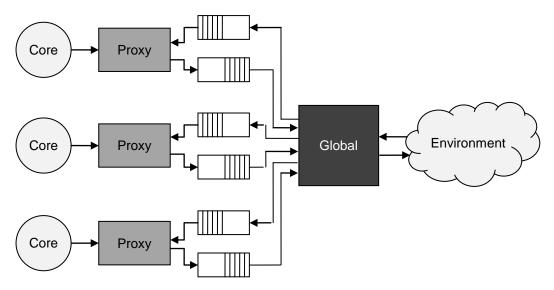

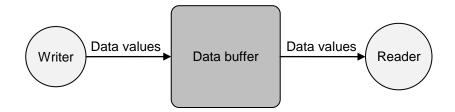

| FIGURE 9.3: EXECUTION JITTER WHEN WAITING FOR THE COMPLETION OF AN ADC    |

| CONVERSION                                                                |

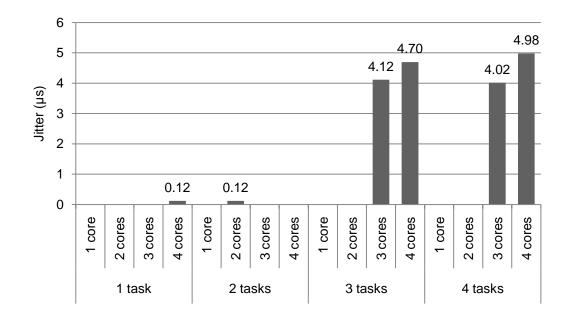

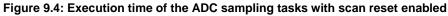

| FIGURE 9.4: EXECUTION TIME OF THE ADC SAMPLING TASKS WITH SCAN RESET      |

| ENABLED                                                                   |

| FIGURE 9.5: JITTER IN SERVICING A PIN ASSERTION REQUEST ON A GLOBAL GPIO  |

| PERIPHERAL                                                                |

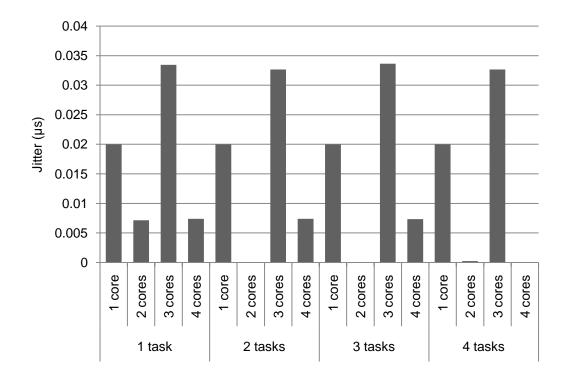

| FIGURE 9.6: HARDWARE UTILISATION WHEN MOVING TO THE RESOURCE SHARING      |

| SCHEME                                                                    |

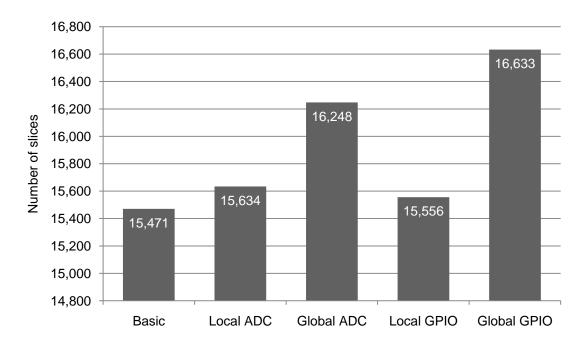

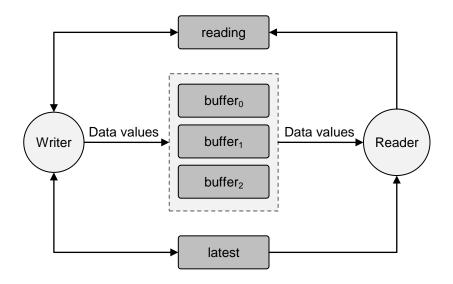

| FIGURE B.1: DATA SHARING BETWEEN ONE WRITER AND ONE READERB-1             |

| FIGURE B.2: A REPRESENTATION OF THE THREE-BUFFER SINGLE-WRITER SINGLE-    |

| READER MECHANISMB-3                                                       |

| FIGURE C.3: OVERVIEW OF AN ELECTRONIC ENGINE CONTROL UNITC-1              |

| FIGURE C.4: TASK TRANSACTION REQUIREMENTSC-3                              |

# List of Tables

| TABLE 3.1: TASK SCHEDULE                                                     | 3-2  |

|------------------------------------------------------------------------------|------|

| TABLE 4.1: TASK SCHEDULE WITH A LONG-TASK                                    | 4-3  |

| TABLE 6.1: EVALUATION TASK-SET WITHOUT A LONG-TASK                           | 6-2  |

| TABLE 6.2: TASK-SET YIELDING SLUGGISH CONTROL (TS-1)                         | 6-3  |

| TABLE 6.3: TASK-SET WITH BETTER CONTROL BUT UNABLE TO HIT FAST MOV           | ING  |

| TARGETS (TS-2)                                                               | 6-3  |

| TABLE 6.4: TASK-SET TO IMPROVE THE ABILITY TO HIT FAST MOVING TARGETS (TS-3  | 3)6- |

| 4                                                                            |      |

| TABLE 6.5: THE RUN-TIME TIMING PROPERTIES OF THE TASKS UNDER TTC-MT $\ldots$ | 6-7  |

| TABLE C.1: TASK TIMING PROPERTIES                                            | C-2  |

# List of Listings

| LISTING 3.1: PSEUDO CODE FOR A TTCA IMPLEMENTATION                             |

|--------------------------------------------------------------------------------|

| LISTING 3.2: SINGLE-RATE CYCLE EXECUTIVE DISPATCH                              |

| LISTING 3.3: MULTI-RATE CYCLE EXECUTIVE DISPATCH                               |

| LISTING 3.4: A TTCA IMPLEMENTATION EVENT SERVICE                               |

| LISTING 3.5: ALLOWING TASKS TO EXCEED THE TICK INTERVAL                        |

| LISTING 3.6: NON-TABLE-DRIVEN MULTI-RATE EXECUTIVE DISPATCH                    |

| LISTING 3.7: RUN QUEUE DISPATCH                                                |

| LISTING 3.8: TABLE-FREE MULTI-RATE EXECUTIVE SCHEDULE CREATION                 |

| LISTING 3.9: TIME-EVENT QUEUE SCHEDULE CREATION                                |

| LISTING 3.10: TIME-EVENT QUEUE DISPATCH                                        |

| LISTING 3.11: ISR FOR THE TICK TIMER WHEN USING THE MTI SCHEDULER              |

| LISTING 3.12: ISR FOR THE TASK TIMER WHEN USING THE MTI SCHEDULER              |

| LISTING 3.13: MTI SCHEDULER DISPATCH                                           |

| LISTING 3.14: ADAPTING THE MTI SCHEDULER DISPATCH SO THAT TASKS CAN            |

| OVERRUN TICKS                                                                  |

| LISTING 3.15: TASK DEFINITION AT A HIGH LEVEL IN THE C PROGRAMMING LANGUAGE 3- |

| 19                                                                             |

| LISTING 3.16: LOW LEVEL TASK WRAPPER IN THE HARDWARE MULTI-RATE EXECUTIVE 3-   |

| 19                                                                             |

| LISTING 5.1: INITIALISATION ON THE TIMING MASTER                               |

| LISTING 5.2: INITIALISATION ON THE TIMING SLAVES                               |

| LISTING 5.3: MANAGING THE RUN QUEUE IN THE SCHEDULED QUEUE                     |

| LISTING 5.4: MANAGING THE RUN QUEUES IN THE SCHEDULING CORE                    |

| LISTING 5.5: EVENT SERVICE OF THE SCHEDULING CORE                              |

| LISTING 5.6: TASK DISPATCH IN A SCHEDULED CORE                                 |

| LISTING 5.7: C CODE FOR ONE OF THE IDENTICAL TASKS IN THE EVALUATION OF INTER- |

| TASK COMMUNICATION                                                             |

| LISTING 5.8: ASSEMBLY CODE FOR A DELAY TASK                                    |

| LISTING B.1: PSEUDO CODE FOR THE THREE-BUFFER SINGLE-WRITER SINGLE-READER      |

| MECHANISMB-4                                                                   |

## **List of Publications**

Athaide, K.F. and Pont, M.J. "**Ameliorating Problems in System Integration with Time-Triggered Scheduling**", Proceedings of the 5th IEEE International Conference on Systems of Systems Engineering (SoSE '10) (Loughborough, UK, 22 – 24 June 2010).

Athaide, K.F. Pont, M.J. and Ayavoo, D. "**Deploying a Time-triggered sharedclock architecture in a multiprocessor system-on-chip design**", Proceedings of the Fourth UK Embedded Forum (Southampton, UK, 9 – 10 September 2008), pp. 96-103. Published by the Institute of Engineering and Technology [ISBN: 978-0-86341-949-2].

Athaide, K.F. Pont, M.J. and Ayavoo, D. "**Shared-Clock Methodology for Time-Triggered Multi-Cores**", Proceedings of the 31st Communicating Process Architectures Conference (York, UK, 7 – 10 September 2008), pp. 149-162. Published by IOS Press [ISBN: 978-1-58603-907-3].

Athaide, K.F. Hughes, Z.M. and Pont, M.J. "**Towards a Time-Triggered Processor**", Poster presented at the third UK Embedded Forum (Durham, UK, 2 – 3 April 2007).

#### Patents

Pont, M.J., Athaide, K.F. and Ayavoo, D. (2007) "**Debug unit for use with time-triggered systems**" (filed UK, 11 May 2007: details awaited).

# **Chapter 1**

## Introduction

"Simplicity is the ultimate sophistication" – so articulated Leonardo da Vinci (1452 – 1519), a sentiment later expressed by Albert Einstein with, "*Everything* should be made as simple as possible, but no simpler!" (Einstein 1933). Yet, in our modern society technology gets ever more complex. In his acceptance speech for the 1980 ACM Turing Award, Hoare remarked that the price of reliability is the pursuit of utmost simplicity, and that it is a price most find "*hard to pay*" (Hoare 1981).

Consider the workflow of an average office worker whose day-to-day activities might involve data entry, envelope stuffing, sitting in meetings, etc. The simplest way to get through them is in a sequential, predefined manner (Sasso 1986; Schultz et al. 2003). Unfortunately, activities in a work day cannot be conducted sequentially due to competing requirements: meetings have to be arranged around all participants' schedules; the need to mail items arises at different points in the day; occurrence of emergencies and so on (Hudson et al. 2002). The worker must then jump from job to job to meet daily deadlines (Rouncejield et al. 1994).

Consequently, simplicity is lost because of the change in mindset required by each job interruption (O'Conaill et al. 1995; Schultz et al. 2003). This is in addition to the time required to prepare for and clean up after a job. For example, data entry would require pulling the keyboard closer and opening a spreadsheet program; envelope stuffing involves clearing space for papers, envelopes and writing materials; meetings require walking to the meeting room and back; and so on. Increased interruptions lead to a loss in reliability due to variability in productivity and/or quality (Schultz et al. 2003; Roper et al. 2007; Haynes 2008) unless made up for during slack time (shortened lunch breaks, overtime, etc.) (Spira et al. 2005).

Additionally, multiple workers doing the same job must also arrange their work times to avoid arguments over company resources. For example, to prevent queues at the printer, workers may arrange to do envelope stuffing at different times. (Gordon et al. 1997)

A straightforward way to remedy the situation is to hire a worker for each job. However, this plainly costs the company in terms of salary even if productivity gains are made (Kim et al. 2004). On the other hand, a worker hired for a particular job does not have to be skilled to do every job and so could be paid less (Sasso 1986), perhaps resulting in a net salary decrease. The real solution, as it almost always is, is a compromise between the two extremes (Kremer et al. 1996).

Henry Ford, whose efforts were *"in the direction of simplicity"* in order to provide *"the very best service and the most convenient in use*", pioneered by equalising and more than doubling daily wages and by employing workers according to their skill and physical handicaps; the former attracted the highest skill in the field and the latter increased production. His efforts also eliminated interruptions in the form of wasteful material and tool hunting with assembly lines. (Ford et al. 1922)

The office situation has parallels in the field of computing where a personal computer, assuming it has only one "brain" like an office with one worker, cannot nonchalantly spend five hours downloading a file before it allows a letter to be typed in a word processor. So the computer has to alternate very, very quickly between downloading the file and allowing the letter to be typed. Each alternation, like the office worker's preparation when interrupted, requires memory to be re-allocated and re-loaded, the appropriate computing instructions to be re-fetched, etc. Also, like the office printer, both of the computer jobs will be "printing" to a common storage device and display device.

In this thesis, a solution to this loss of reliability in the field of *embedded computing* is explored by the application of a proven methodology in order to maintain programming simplicity: the exploration being inspired by the recent and rapid adoption of multi-core technology (Borkar 2007) and by the statement that "*the simple and elegant systems tend to be easier and faster to design and get right, more efficient in execution, and much more reliable*" (Dijkstra 1997). Colloquially, the task of keeping an office worker's jobs simple and interruption-free (and hence reliable) is explored by hiring a superhuman worker with more than one brain.

#### 1.1 Embedded Computing

In computer science, the field of embedded computing studies *embedded processor cores*. These are like their desktop and server variants in that their behaviour can be modified by software; but are different in that they have a longer life cycle, are designed for harsher environments and have lower power consumption. Embedded processor cores are often included with mechanical

and other parts, forming an *embedded system*, the forerunner to tomorrow's cyber-physical system (Lee 2009).

"Embedded" is used to indicate that the presence of the system is unapparent to the end user rather than imposing constraints on physical size, though, undeniably, smaller sizes may facilitate the concealment. It also indicates that the system is part of a larger system or product whose primary functionality need not be as a computer, as in the case of an antilock braking system in a car (Pont 2002; Wolf 2002; Ganssle 2003). Such a system is designed to perform a small number of dedicated functions albeit with choices and different options, i.e. the end-user can make choices concerning functionality but cannot change the functionality of the system by adding/replacing software (Sachitanand 2002; Heath 2003).

Embedded systems have proliferated into our daily lives, being present in televisions, cars, aircraft, Automated Teller Machines (ATMs), etc., and even in such mundane products as ovens, toasters and dishwashers. Soon even engineers will be hard put to identify embedded systems due to the improbability of being able to squeeze in all the required features and intelligence into tiny devices. This can be seen already in contactless payment cards (Olsen 2007) or in car tyres that communicate wirelessly with the vehicle about road conditions, tyre inflation, temperature, etc (Ergen et al. 2009). These systems will soon be woven into everything we touch, including fabrics (Kim et al. 2009).

Already by 2000, 98% of the computing devices sold worldwide were embedded devices (Borriello et al. 2000). The number is expected to reach 16 billion for

this year (nearly 3 embedded devices per person on earth) and to exceed 40 billion in 2020 (Helmerich et al. 2005; ARTEMIS SRAWG 2006). In addition, the global market is expected to increase from £63.3 billion in 2008 to an estimated £77.3 billion by the end of 2013 (Joshi 2009); and expenditure on software research and development is expected to increase from £47.9 billion in 2002 to £109.0 billion in 2015 (Helmerich et al. 2005; Alves 2007).

#### 1.2 Real-time embedded systems

Embedded systems are frequently required to have real-time behaviour, that is, they have to produce an action in response to a stimulus within a specified time interval, independently of how quickly the action is performed (Buttazzo 2002a). Outside of this interval, the result, even if correct, is marginally or completely useless (Audsley et al. 1990). In *safety-critical* real-time systems, safe performance or operation is essential and errors or malfunctions arising due to the failure of real-time behaviour can result in death, injury or illness, major economic loss, mission failure, environmental damage or property damage (Dimond et al. 2002). This description clearly fits systems used in industrial automation, medical equipment, nuclear power plants, avionics and automobiles, amongst others (Redmill 1992; Profeta III et al. 1996).

By their nature, safety-critical systems are expected to be as *dependable* as possible. Dependability is the trustworthiness of a computer system such that reliance can justifiably be placed on its behaviour (Laprie 1992) and subsumes reliability, availability, integrity, maintainability, etc. (Avižienis et al. 2004). It is an assessment shaped by social and psychological factors in addition to hard statistics.

This thesis concerns itself with two aspects of dependability in safety-critical systems; *reliability*, which is the ability to provide a required service, according to stated specifications, for a time under varying operating conditions (IEEE 1990; Laprie 1992); and, *maintainability*, which is the ease with which modifications can be made to correct faults, improve performance or other attributes, or adapt to a changed environment (IEEE 1990). Maintainability, like reliability, assumes that the environmental conditions declared by the system specifications always holds and is differentiated from *robustness* which indicates tolerance to unexpected conditions (IEEE 1990).

#### **1.3 The time-triggered co-operative architecture**

Among the myriad of ways to build real-time systems (Fidge 2002; Sha et al. 2004; Buttazzo 2005a), this thesis focuses on the simple, reliable time-triggered co-operative architecture (TTCA) (Pont 2001). It has been found to be a good match for a wide range of applications, such as automotive applications (Ayavoo et al. 2004; Short et al. 2005), wireless (ECG) monitoring systems (Phatrapornnant et al. 2006), various control applications (Edwards et al. 2004; Key et al. 2004; Bautista et al. 2005; Nghiem et al. 2006), data acquisition systems, washing-machine control and monitoring of liquid flow rates (Pont 2002).

The co-operative nature of TTCA simplifies software development and facilitates more emphatic guarantees of the quality of interaction with the environment; both, of which make it a reliable architecture. But this nature is simultaneously a big impediment that necessitates an accurate estimation of software execution times. Software non-determinism (from branching, variable

number of iterations and dependence on environmental events) and hardware non-determinism (from caches, direct-memory-access) hinder such estimations.

In addition, software that takes too long to execute can adversely affect system responsiveness, even if such software runs infrequently, e.g. software that runs every ten hours but takes two hours to execute stops the system from doing anything else for those two hours. This then imposes a severe constraint that all software must execute quickly in order to maintain system response times (Allworth 1981; Locke 1992).

In most cases, execution time is not a single value, but a range. In such cases, TTCA exposes fragility if the upper bound of the range is too liberal; leading to an excessive waste of resources. Conversely, conservative estimates potentially throw the entire system off temporally. While techniques have been developed to deal with such failures, they can be counterproductive due to increased complexity and/or the introduction of unknown states into the system (Locke 1992; Kalinsky 2001; Hughes et al. 2008).

TTCA has also been criticised for requiring exhaustive validation and testing during design and maintenance (Liu et al. 1995), both of which are timeconsuming and costly. However, given that the cost of unanticipated changes to software increases exponentially as systems age (Griswold et al. 1993), perhaps this extra scrutiny is a blessing in disguise.

Another consequence of co-operative execution and software and hardware non-determinism is that only the software immediately after the triggering event can be guaranteed a start time with minimum variance. All other software is affected by the cumulative variance of the execution times of all software that executed prior in the same occurrence of the triggering event (Kalinsky 2001).

For these reasons, TTCA has been relegated as an ideal – suitable for only the simplest systems. For everything else, compromises have been made. Commercial system software vendors have also moved on, so that when building a new design or updating an old one, commercial off-the-shelf and standard operating systems are frequently adopted that do not support cyclic scheduling (Liu et al. 1995; Xu et al. 2000).

#### 1.4 Aims of the thesis

The aims of this thesis are to increase the number of *feasible* variants of the single-processor time-triggered co-operative architecture (TTCA) and to increase the temporal quality (i.e. reliability) of responses of TTCA to environmental stimuli. Increasing the number of feasible variants decreases the chance that maintenance will result in an unfeasible design while the use of TTCA will reduce the amount of time needed to understand the program in the maintenance activity.

These aims will be pursued by increasing the concurrency in the system whilst maintaining the design simplicity of software that expects a non-concurrent system.

#### 1.5 Scope

This thesis possesses the following scope:

• The techniques operate on *one* particular software processing core in a real-time system. Any other cores are considered together with the

environment of the system to form the environment of the core. The core may be the sole core in a processor or may be one of several (possibly heterogeneous) cores in a multi-core processor.

- The software executing on the core is expected to run at a fixed rate, to complete execution before a certain time, to have a bounded execution time, and to behave in a highly predictable manner (Stankovic 1988; Stankovic et al. 1990; Spuri et al. 1995; Buttazzo 2005a).

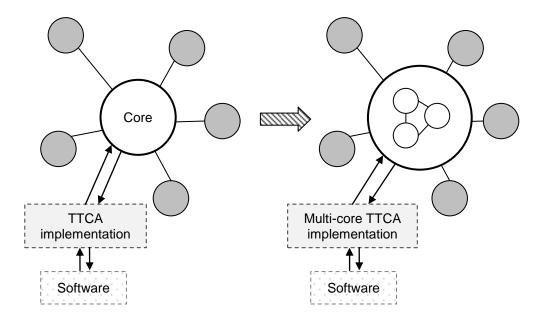

- The transformation under consideration in this thesis will result in the core being converted into a network of cores (Figure 1.1) changing neither the software application programming interface (API) nor the input/output (I/O) interface with other hardware.

Figure 1.1: The transformation will replace a single-core processor with a multi-core one that preserves the I/O interface with other hardware and the software API.

### **1.6 Key contributions**

This thesis makes the following contributions to increase the applicability of the time-triggered co-operative architecture:

- The first contribution is a novel processor for single-processor TTCA designs that are either unfeasible or impractical due to the presence of software with heavy utilisation and the presence of non-harmonic relationships in software execution rates. This has been achieved by increasing the number of available processing elements, without affecting the application software design. This contribution also has the benefit of reducing the probability of defects being introduced by the maintenance of feasible single-processor TTCA designs.

- The second contribution extends an existing TTCA hardware implementation to work with the new processor. This contribution results in a TTCA implementation that possesses zero scheduler overheads and the ability to execute heavily utilised or non-harmonically related software, in addition to better maintainability and a greater scope for future development.

- The third contribution uses existing software techniques to infuse jitter reduction capabilities into the non-concurrent TTCA hardware and the concurrent version from the implementation previous contribution. This contribution results in a TTCA implementation with zero task release jitter in addition to zero scheduler overheads, the ability to execute heavily or non-harmonically utilised software, better maintainability and a greater scope for future development.

- The fourth contribution is a hardware technique that allows peripherals to be accessed deterministically and concurrently without blocking whilst maintaining their consistency. This contribution eliminates the need for

the gateway tasks inherent in the TTCA implementations of the previous contributions.

• The fifth contribution is a processor core for purely co-operative software that does not suffer from jitter or lengthened latency due to the interrupt servicing, while continuing to provide the system scheduler with flexibility in schedule creation and in the order in which tasks are dispatched.

#### **1.7 Thesis overview**

Chapter 2 provides an overview of the software architecture for real-time systems, such as scheduling and resource sharing. The task model used for the hard real-time systems under consideration in this thesis is also described along with an account of latency and jitter and the reason they may give rise to problems in a system.

Chapter 3 provides an overview and execution model of TTCA along with the description of several software implementations and one hardware implementation. The problems that arise from use of TTCA are elaborated in Chapter 4 along with the solutions that have been proposed for these problems and the discrepancies that they possess.

Chapter 5 presents a novel multi-core processor to alleviate the problems of single-processor TTCA designs. The chapter also describes the wait-free loop-free inter-core communication scheme and the scheduler extensions that were made to allow standard TTCA application design to be used with the processor. Chapter 6 presents a case study that examines the maintenance effort required and the cost if a F16 flight system were initially deployed on a single-core

processor with an appropriate scheduler versus the multi-core processor described in Chapter 5.

Next, Chapter 7 incorporates the scheduler extensions of the multi-core processor into an existing TTCA hardware implementation in a successful attempt at achieving zero scheduler overhead and zero task release jitter. Chapter 8 then presents a case study that examines the migration of an existing co-operative system with many small communicating tasks to the presented multi-core platform and the effects this has on the tasks' execution properties.

Chapter 9 introduces a hardware technique to share resources that communicate with the environment, using a simple but novel technique to increase determinism in accessing these resources.

Finally, Chapter 10 concludes with a final summary, with a discussion of limitations and with the consideration of future work that may be performed.

#### **1.8 Conclusions**

The intuitive notion that productivity is increased by concentrating on a single task is not only demonstrative in the work place but is also reflected in software design. Particularly, a software developer's development productivity increases if software is written in the co-operative manner of execution. In the safety-critical field, co-operative execution can be coupled with the highly predictable time-triggered architecture to produce the time-triggered co-operative architecture (TTCA) that provides a simple and intuitive interface for application development.

Unfortunately, in the same way that an office worker is often impelled by daily deadlines to abandon simpler ways of working, so also is an embedded systems designer often impelled by real-time constraints to abandon a TTCA implementation. Alternative real-time designs are able to accommodate the constraints, but usually end up compromising on predictability or on the quality of environmental interactions or on the ease of application development.

This thesis, then, presents research aimed at accommodating some of the stricter real-time constraints on TTCA – expanding the range of designs that can be built on this architecture. The next chapter will examine, in greater detail, how the software for real-time systems is constructed and the various design choices involved.

## **Chapter 2**

# Software architecture of real-time system schedulers

#### **2.1 Introduction**

In real-time computing, the correctness of a system depends both on the logical result of a computation and on the time at which the results are communicated to the environment (Stankovic 1988; Ramamritham et al. 1994). Besides requiring that the logical result be computed before it is communicated, real-timeliness places no other constraint on the computation speed. Predictability is the foremost goal in these systems (Stankovic 1988; Stankovic et al. 1990; Buttazzo 2005a). These systems have a long life-cycle and a perennial uptime, i.e. no restarts are required unless necessitated by a maintenance or upgrade cycle (Koopman 1996).

The software design for these systems is concerned with enforcing the real-time constraints on the scanning of sensors and on the driving of actuators (non-reactive systems log data instead). The application design process leverages the support of a real-time operating system (RTOS) that may also: provide fault tolerance and distribution; and integrate time-constrained resource allocations and scheduling across a spectrum of resources, e.g. sensor processing, communications, etc. This chapter explores some of the design decisions of the RTOS components that manage the execution of application software and that manage the access to resources that connect to the environment.

The next two sections discuss the characteristics of a real-time system's interaction with its environment and the level of quality required from such interaction based on the system's classification. This is followed by a brief description of the hardware model of a typical real-time system and a more indepth software model. The last few sections briefly examine resource management and scheduling.

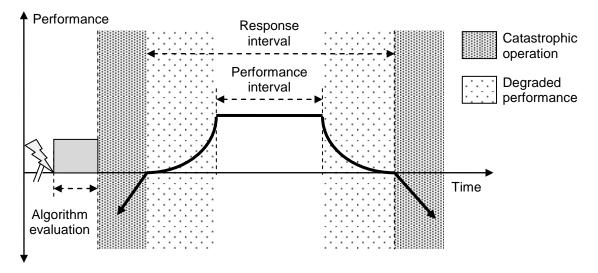

#### 2.2 Environmental interaction

Every reactive real-time system may be considered a control system: the system measures one or more environmental properties and responds (via realtime actions or responses) by algorithmically bringing one or more of these properties to desired states. The numerical or logical effects of the actions are constrained by the application design to an interval in which they must be used (the response interval) and to an interval in which the desired performance is obtained (the performance interval) as seen in Figure 2.1. The upper bound of the performance interval is the *deadline* of the response. (Audsley et al. 1990; Buttazzo 2005a)

It is quite common for the design of a real-time embedded response to have an infinitesimally small, fixed-position performance interval, implying that the response must be *time deterministic* i.e., for every timed input stream, a unique timed output stream will be provided (Henzinger et al. 2003; Kopetz 2008). In other words, the temporal and the logical properties of a response should be determinable in finite time through design analysis under all assumed conditions, i.e. that these properties should be *predictable*.

In some literature, the desired time determinism is ambiguously referred to as "predictability" and *determinism* is just as ambiguously used to refer to the degree to which a system's exact execution sequence can be predicted ahead of time, i.e. *execution determinism* (Locke 1992; Stankovic et al. 1993; Bate 1998). Execution determinism has been found sufficient, though not necessary, to achieve time determinism (Locke 1992; Stewart 2001; Henzinger 2008). On the other hand, undisclosed implementation details that affect observable system behaviour or *observable implementation determinism* is crucial for reliable behaviour and is often given the sole importance (Engel et al. 2004; Henzinger 2008).

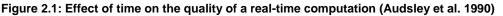

The range of the performance interval indicates the tolerated *variance* or *jitter* in the real-time action while the position of the response interval indicates the tolerated *latency*. Increases in the latency of responses inversely affect the system responsiveness and may degrade control performance and cause system instability (Kim et al. 1997). Depending on the application, jitter may also seriously impact performance: it may cause instability due to a variable sampling period (Locke 1992); it may introduce errors significant enough to render a sampled signal meaningless (Cottet et al. 1999); it may need to be