# Application of Search-Based Software Testing in Stress-Testing of Deeply Embedded Components in Integrated Circuits

Thesis submitted for the degree of

Doctor of Philosophy in Computer Science

at the University of Leicester by

**Basil Eljuse**

Department of Informatics March 2020

# Abstract

# Application of Search-Based Software Testing in Stress-Testing of Deeply Embedded Components in Integrated Circuits Basil Eljuse

Modern Integrated Circuits (ICs) based system design have evolved over time to support the ever demanding complex use-cases. As more functionality is packed into these ICs, there are more deeply embedded components present in these ICs. The performance of these deeply embedded components are critical in ensuring the final system behaviour. By virtue of being deeply embedded they are intrinsically difficult to test - especially in system context. This thesis is focused on the task of 'stress testing' an IC in its operational environment with the goal of identifying any circumstances under which the circuit might suffer from performance issues. It addresses how search-based algorithms provide an automated approach in testing these ICs. Here it establishes that with a suitable search-space representation search-based approaches can be applied in stress-testing of complex ICs. Here it outlines how a simple hill-climbing based search algorithm is successfully used to generate tests in an automated manner. It also studies the application of more advanced search-based algorithms like random-restart hill-climbing and simulated annealing in addressing this testing challenge. As system behaviour of complex ICs can be affected in multiple ways, this research investigates the application of multiobjective algorithms in this context. It shows that a multi-objective algorithm like Strength Pareto Evolutionary Algorithm 2 (SPEA2) is able to generate better stress tests, maximising multiple objectives. The empirical studies performed as part of this thesis are conducted on Arm<sup>®</sup> Cache Coherent Interconnect (CCI), which provides cache coherency and interconnect functionality on modern Arm based systems. It concludes that search-based software testing approaches are indeed suitable for addressing testability challenges posed by modern ICs especially at system level and provide ways to generate better stress tests.

# Dedication

I dedicate this to my loving God for all the blessings thou showered upon me. I also dedicate this to my parents, wife, son, daughter and everyone who supported me through this journey. Nothing would have been possible without their unwavering support, unlimited patience and enduring love, for which I am eternally thankful.

# Acknowledgements

I would like to start expressing my sincere gratitude to my guide Dr. Neil Walkinshaw for all the support and guidance during my research. I would also like to thank Dr. Jose Miguel Rojas Siles and Prof. Reiko Heckel for all the support during my studies. I am sincerely grateful to Dr. Fer-Jan de Vries, the postgraduate tutor at the Informatics department (University of Leicester), who helped me through the intermediate stages of my study.

I would like to thank Arm Ltd for the support extended to me during this study, while being employed there. In particular, I would like to thank Guillaume Letellier and James King for the internal reviews they conducted in relation to this study. I would also like to thank all my line managers during this period, the HR, the Intellectual Property team and the Legal team at Arm for their support during my study period. I want to express a special note of thanks to a couple of my colleagues at Arm - Sudeep Holla and Punit Aggarwal - who helped me with some of the kernel driver details, which were crucial during the experimentation phases of my research.

The earliest support for my higher studies came as reference letters for my admission from my teachers Dr. Chitra Prasad and Dr. Ansamma John. I would like to express my sincere gratitude to both of them. Many of my friends and family showed keen interest in tracking the progress I was making and thanks a lot for all the encouragements from them - it meant a lot to me.

# Contents

| 1        | $\mathbf{Intr}$ | roduction                                                        | 11 |

|----------|-----------------|------------------------------------------------------------------|----|

|          | 1.1             | Introduction                                                     | 11 |

|          | 1.2             | Specific Contributions                                           | 13 |

|          | 1.3             | Thesis Outline                                                   | 13 |

|          | 1.4             | Contributory Publications                                        | 15 |

| <b>2</b> | Bac             | kground                                                          | 16 |

|          | 2.1             | Testing - A Perspective on Industry Practices                    | 16 |

|          | 2.2             | IC Development: Understanding the Testing Context                | 20 |

|          | 2.3             | CCI: Details and Testing Challenges                              | 23 |

|          |                 | 2.3.1 Understanding Cache Coherency and Role of CCI in IC Design | 23 |

|          |                 | 2.3.2 CCI in Real System Designs - TC2 and Juno                  | 25 |

|          |                 | 2.3.3 CCI: Current Testing Practices and Challenges              | 28 |

|          | 2.4             | Problem Statement                                                | 29 |

|          | 2.5             | Search-Based Software Testing (SBST)                             | 32 |

|          |                 | 2.5.1 Related Research                                           | 32 |

|          |                 | 2.5.2 SBST: Solution Options                                     | 34 |

|          | 2.6             | Summary                                                          | 38 |

| 3        | Sea             | rch-Space Model and Experimentation Framework                    | 39 |

|          | 3.1             | Understanding the Problem Domain                                 | 40 |

|          | 3.2             | Initial Search-Space Model                                       | 41 |

|          |                 | 3.2.1 Applying Hill-Climbing with Search Grid                    | 42 |

|          |                 | 3.2.2 Applying Genetic Algorithm with Search Grid                | 44 |

|          | 3.3             | Final Search-Space Model                                         | 47 |

|          |                 | 3.3.1 Payload Size $PS$ :                                        | 48 |

|          |                 | 3.3.2 Sparsity $SP$ :                                            | 49 |

|          |                 | 3.3.3 Actor Profile $AC$ :                                       | 49 |

|          |                 | 3.3.4 The Fitness Function                                       | 50 |

|          | 3.4             | Experimentation Framework                                        | 51 |

|          |                 | 3.4.1 Experimental Setup Details                                 | 55 |

|              | 3.5 Summary                                                                                           |       | 57        |

|--------------|-------------------------------------------------------------------------------------------------------|-------|-----------|

| 4            | Suitability of Search-based Algorithms in IC Testing                                                  |       | <b>58</b> |

|              | 4.1 Hill-Climbing Approach                                                                            |       | 59        |

|              | 4.2 Methodology                                                                                       |       | 61        |

|              | 4.3 Results and Discussion                                                                            |       | 63        |

|              | 4.4 Threats to Validity                                                                               |       | 65        |

|              | 4.5 Summary                                                                                           | <br>• | 66        |

| <b>5</b>     | Applying Advanced Search-based Algorithms in IC Testing                                               |       | 67        |

|              | 5.1 Use of Advanced SBST Algorithms                                                                   |       | 67        |

|              | 5.2 Methodology $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$               |       | 72        |

|              | 5.3 Results $\ldots$ |       | 74        |

|              | 5.4 Threats to Validity                                                                               |       | 78        |

|              | 5.5 Summary                                                                                           | <br>• | 79        |

| 6            | Improving IC Testing with Multi-Objective Algorithms                                                  |       | 80        |

|              | 6.1 Use of Multi-Objective SBST Algorithms                                                            |       | 80        |

|              | 6.2 Methodology $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$               |       | 83        |

|              | 6.3 Results                                                                                           |       | 87        |

|              | 6.4 Threats to Validity                                                                               |       | 92        |

|              | 6.5 Summary                                                                                           | <br>• | 92        |

| 7            | Conclusion and Future Work                                                                            |       | 94        |

|              | 7.1 CCI Testing Improvements with SBST                                                                |       | 94        |

|              | 7.2 Implications for Future IC Testing                                                                |       | 96        |

|              | 7.3 Future Research Direction                                                                         | <br>• | 97        |

| A            | Early Search-Space Model Trials                                                                       |       | 99        |

|              | A.1 Genetic Algorithm based Experiments                                                               |       | 99        |

|              | A.1.1 Algorithm                                                                                       |       | 99        |

|              | A.1.2 Results                                                                                         | <br>• | 100       |

| в            | Algorithm Parameter Evaluation                                                                        | 1     | 103       |

|              | B.1 Grid Approach                                                                                     |       | 103       |

| $\mathbf{C}$ | Implementation Project                                                                                | 1     | 105       |

|              | C.1 Project Details                                                                                   |       | 105       |

# List of Tables

| 3.1 | Sparsity Definition                                                    | 49  |

|-----|------------------------------------------------------------------------|-----|

| 3.2 | Sparsity                                                               | 54  |

| 3.3 | Actor profile - TC2 platform                                           | 54  |

| 3.4 | Actor profile - Juno platform                                          | 54  |

| 5.1 | Wilcoxon signed-rank test (p) & Effect Size (es) - Data Stall Cycles . | 75  |

| 5.2 | Wilcoxon signed-rank test (p) & Effect Size (es) - score gain & AUC    | 76  |

| 6.1 | SPEA2 parameter tuning attributes                                      | 86  |

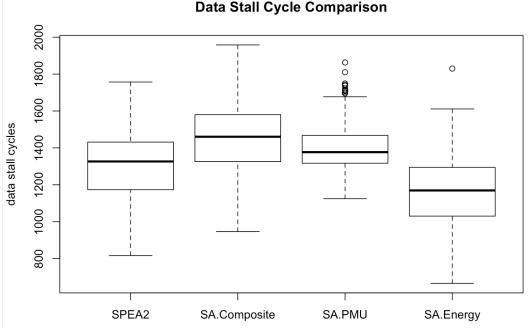

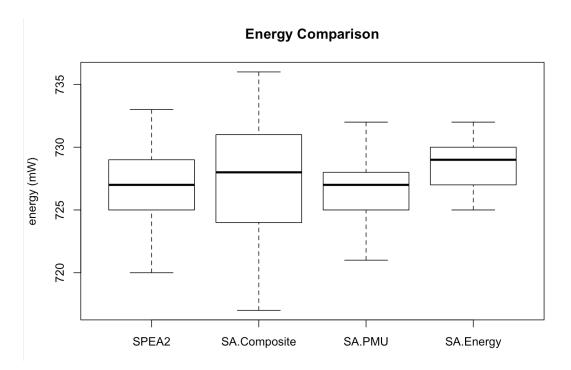

| 6.2 | Wilcoxon signed-rank test (p) & Effect Size (es) - Data Stall Cycles   |     |

|     | & Energy Comparisons                                                   | 90  |

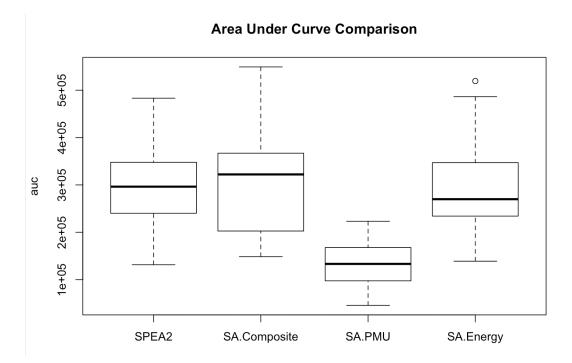

| 6.3 | Wilcoxon signed-rank test (p) & Effect Size (es) - AUC $\hdots$        | 91  |

| B.1 | SPEA2 Parameter Evaluation - Grid Approach                             | 104 |

| C.1 | Project - LoC Details                                                  | 105 |

# List of Figures

| 2.1 | Hardware-Software Co-Design: A typical workflow                             | 21 |

|-----|-----------------------------------------------------------------------------|----|

| 2.2 | CCI States - details                                                        | 24 |

| 2.3 | Juno platform with CCI-400.                                                 | 26 |

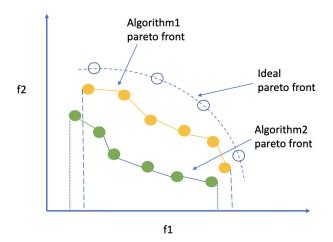

| 2.4 | Solution candidates at pareto front                                         | 37 |

| 3.1 | Cache memory operations defined as search grid                              | 42 |

| 3.2 | Genetic Algorithm - components and control flow.                            | 46 |

| 3.3 | Experimental setup with search-based algorithms for CCI testing $\ . \ .$   | 53 |

| 3.4 | Juno platform Details                                                       | 56 |

| 3.5 | Physical Setup                                                              | 56 |

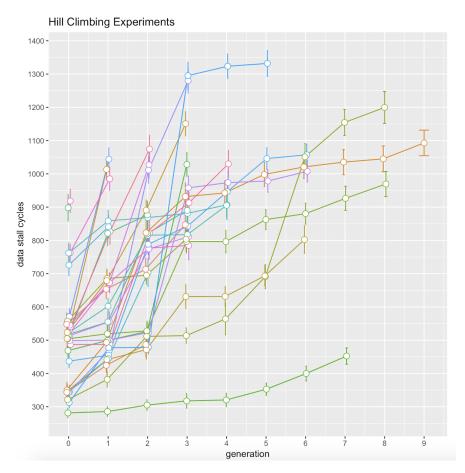

| 4.1 | Hill-Climbing scores. 30 experiments showing how different experi-          |    |

|     | ments hit local maxima                                                      | 63 |

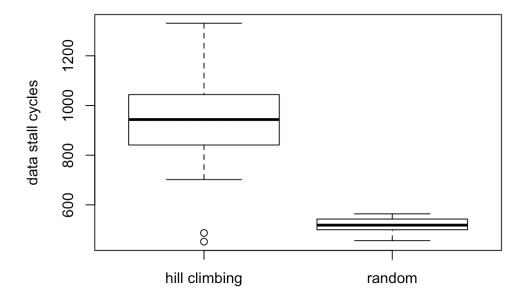

| 4.2 | Hill-Climbing scores. Hill-climbing generated better scores than equiv-     |    |

|     | alent random test generation experiment                                     | 64 |

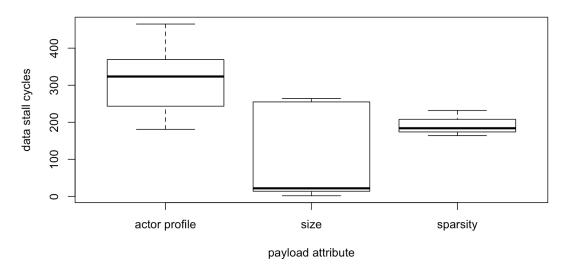

| 4.3 | Sensitivity of payload attributes. Each payload attribute evaluated in      |    |

|     | isolation                                                                   | 65 |

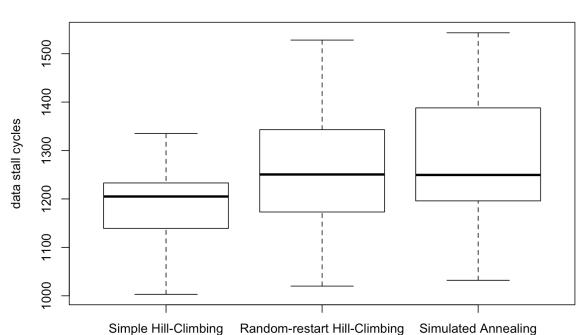

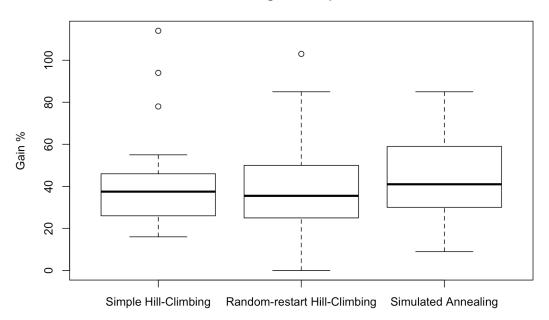

| 5.1 | Data stall cycle comparison Random-restart Hill-Climbing vs Simu-           |    |

|     | lated Annealing vs Simple Hill-Climbing                                     | 75 |

| 5.2 | Gain comparison Random-restart Hill-Climbing vs Simulated Anneal-           |    |

|     | ing vs Simple Hill-Climbing                                                 | 76 |

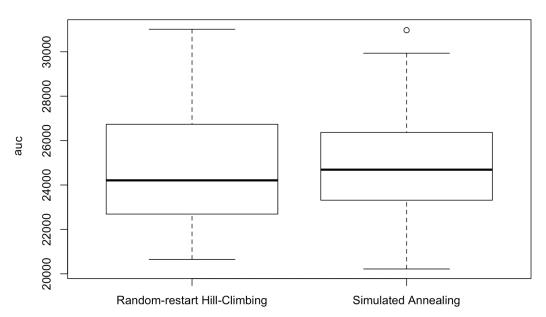

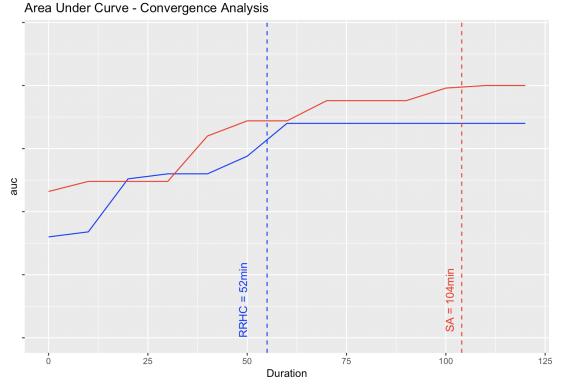

| 5.3 | Area under curve for best scores found across payloads evaluated. $\ . \ .$ | 77 |

| 5.4 | Area under curve - RRHC vs SA - convergence analysis                        | 78 |

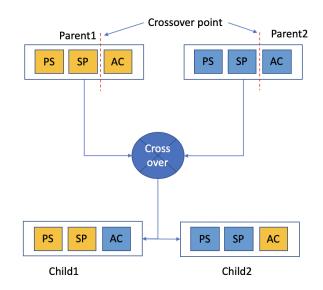

| 6.1 | Crossover Operation                                                         | 82 |

| 6.2 | AUC comparison based on solutions at pareto front: AUC(Algorithm1)          |    |

|     | > AUC (Algorithm2)                                                          | 85 |

| 6.3 | Data Stall Cycles Comparison SPEA2 vs Simulated Annealing - Com-            |    |

|     | posite FF vs Simulated Annealing - PMU FF vs Simulated Annealing            |    |

|     | - ENERGY FF                                                                 | 88 |

| 6.4 | Energy Comparison SPEA2 vs Simulated Annealing - Composite FF                                                                                          |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|

|     | vs Simulated Annealing - PMU FF vs Simulated Annealing - EN-                                                                                           |

|     | $ERGY FF \qquad \dots \qquad 89$                                                                                                                       |

| 6.5 | Area Under Curve Comparison SPEA2 vs Simulated Annealing -                                                                                             |

|     | Composite FF vs Simulated Annealing - PMU FF vs Simulated An-                                                                                          |

|     | $nealing - ENERGY FF \qquad \dots \qquad 91$                                                                                                           |

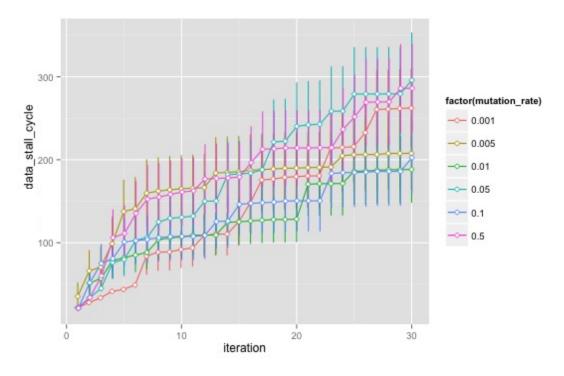

| A 1 | Effect of Metation note                                                                                                                                |

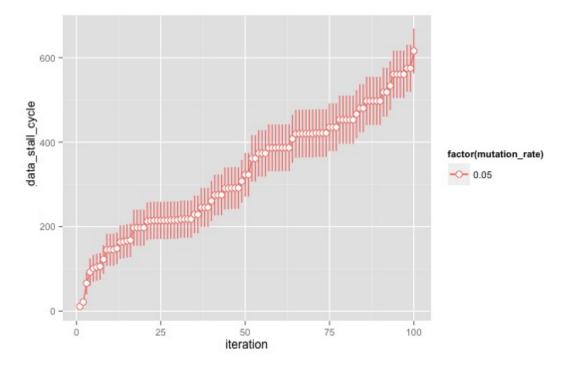

| A.1 | Effect of Mutation rate                                                                                                                                |

| A.2 | GA with mutation rate set to 0.05. $\dots \dots \dots$ |

## Acronyms

- **ADB** Android Debug Bridge.

- AMBA Advanced Microcontroller Bus Architecture.

- **APFD** Average Percentage Faults Detected.

- AUC Area Under the Curve.

- **AXI** Advanced eXtensible Interface.

- **CCI** Cache Coherent Interconnect.

- **CCIX** Cache Coherent Interconnect for Accelerators.

- **CPU** Central Processing Unit.

- DfT Design for Testability.

- E2E End-2-End.

- **EDA** Electronic Design Automation.

- FPGA Field Programmable Gate Array.

- **GP** Genetic Programming.

- GPU Graphics Processing Unit.

- HC Simple Hill-Climbing.

- HIL Hardware-In-the-Loop.

- **IC** Integrated Circuit.

- IO Input-Output.

- **IP** Intellectual Property.

L1 Level1.

L2 Level2.

L3 Level3.

**MCM** Memory Consistency Model.

**NSGA2** Non-dominate Sorting Genetic Algorithm 2.

**PCB** Printed Circuit Board.

**PESA** Pareto Envelop-based Selection Algorithm.

**PMU** Performance Monitoring Unit.

**RAD** Rapid Application Development.

**RRHC** Random-Restart Hill-Climbing.

**SA** Simulated Annealing.

**SBST** Search-Based Software Testing.

**SMC** Static Memory Controller.

**SMD** Standardised Mean Difference.

SoC System-on-Chip.

**SPEA** Strength Pareto Evolutionary Algorithm.

**SPEA2** Strength Pareto Evolutionary Algorithm 2.

TC2 Test Chip2.

**UART** Universal Asynchronous Receiver Transmitter.

**USB** Universal Serial Bus.

**UUT** Unit Under Test.

# Chapter 1

# Introduction

#### 1.1 Introduction

An IC is an electronic circuit design fabricated on a semiconductor material like silicon. ICs form the basic building blocks with which complex electronic systems are designed. Modern ICs offer greater functional capabilities and typically are designed in a modular fashion. It normally comprises of various individual subsystems often interconnected with core components that are deeply embedded in nature. Even though early IC designs had only limited capabilities, modern ICs do pack complex functionality in it that is needed to support the computing demands of modern era.

Testing forms an integral part of the engineering process followed in the development of electronic systems. In the simplest form, testing can be defined as the process of checking whether a given Unit Under Test (UUT) is performing its intended functionality and to identify any potential malfunctions. In case of the engineering process involved in developing ICs, a considerable amount of resources are spent on the testing related activities. This signifies the importance of testing in general.

Computing is becoming more pervasive and is present everywhere. On one hand, it can be found in a tiny sensor at many industrial premises performing instantaneous measurements, while on the other it can be in a supercomputer that performs exascale computing as part of some complex modelling and simulation activity. It can be found in a wearable computing device, a self-driving car or in the cloud infrastructure which powers the modern internet, just to list a few. This wide range of technology is made possible by the advancements in electronic system designs that are built on ICs. So testing ICs is incredibly important considering the extent of impact it has now-a-days. Insufficient levels of testing of ICs could lead to potential malfunctions which can have far-reaching consequences. These malfunctions could manifest in ways that can affect precise functional correctness of computations performed - as it happened in case of Intel's Pentium FDIV (floating point division) bug [Ede97] that resulted in a rare occurrence of incorrect computation during operation. There are other occasions where malfunctions could be fatal - as it happened in case of Intel's F00F bug [Wik], where once triggered it could result in the system to be locked up and needing a hard reboot to revive from that locked-up state. The recent security vulnerabilities around Spectre [Koc+19] and Meltdown [Lip+18] which undermines data privacy shows the extend of damage such malfunctions in ICs or poor design choices can lead to. This affected a wide range of processor architectures - Intel, Arm, AMD etc. These issues elevate the role of testing in modern IC development to levels higher than ever before.

Testing of ICs is demanding and is particularly difficult at a system level. Many of the IC components are considered as 'deeply embedded' and when tested from system level they are under multiple layers of software and hardware components. An IC component is characterised as 'deeply embedded' based on the fact that a hardware component could be performing a highly specialised functionality with very little or no direct interfaces to higher level software in the system. This absence of direct interfaces makes the testing of these components difficult at system level. This results in a key testing challenge for complex systems that are based on these IC designs. One of the testing challenges in general with embedded components is the difficulty of understanding the right context in which it is integrated in a system. In this particular research we focus on testing of an embedded component in its fixed system context. However this same component could be integrated in different configurations based on the possible variations in the final system design. The levels of increasing functional complexity and the high degree of configurability of these hardware components exacerbates the testing challenge further and addressing this forms the key focus of this research.

System testing has a particular significance in IC testing. Due to the nature of development of hardware and software components in IC development (where these two components get developed in parallel), system testing is the earliest opportunity where a full software stack can be tested on a final hardware. This often uncovers complex system integration defects, system performance issues due to incorrect configurations or sub-optimal tuning and also latent defects that can affect the overall system behaviour. Hence this presents us with the last opportunity to uncover and fix such issues which can be exposed only in a final system testing context. With the significance of system level testing on IC development, this research addresses the testing challenges posed specifically by deeply embedded IC components with full End-2-End (E2E) software stack. Even though these deeply embedded IC components are tested in isolation for functional correctness, considering their critical nature in determining the final system behaviour, this research looks at improving

the system test capabilities.

### 1.2 Specific Contributions

The specific contributions of this research are:

- 1. The testing of deeply embedded IC components at system level pose testability challenges which makes traditional test approaches less effective. This research investigates the suitability of search-based algorithms to stress test deeply embedded IC components at system level. This research performs empirical studies, as described in Chapters 4, 5 and 6, that focus on stress testing of a deeply embedded IC component from Arm called CCI.

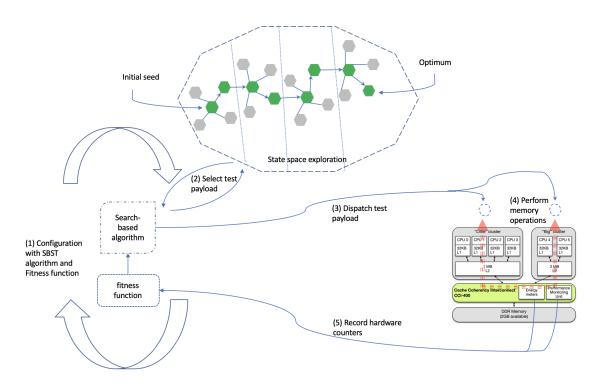

- 2. A proposed search-space representation and a suitable set of relevant fitness functions to perform stress testing of CCI IC component on Arm platforms as described in Section 3.3 of Chapter 3. This research also describes an experimentation framework outlined in Section 3.4 which is used to implement the proposed test approach for conducting the empirical studies.

- 3. Assessment of the relative benefits of applying a set of distinct search-based algorithms to this testing problem. This research conducts empirical studies that assess the application of both single objective and multi-objective search-based algorithms for CCI testing as described in Chapter 4 and 6 respectively. It also looks at addressing local maxima problem observed with the application of local search algorithms with the use of more advanced algorithms adept to overcome a fitness landscape that have multiple local maximas as seen from Chapter 5.

#### 1.3 Thesis Outline

The main body of this thesis consists of seven chapters. Followed by the introduction in the **Chapter 1 - Introduction** (current chapter), the **Chapter 2 -Background** provides a comprehensive background into this research. This section aim to introduce the general background to IC development and how engineering development practices and testing in particular is applied in that context. We explore the specific details of CCI in a full system context and the associated testing challenges. This chapter details the motivation for this research and provides a clear articulation of the problem statement with a pointer to the possible direction in applying search-based test techniques while seeking a solution for this research problem. Chapter 3 - Search-Space Model and Experimentation Framework lay down the essential parts of the proposed solution in addressing the IC testing challenge taken up by this research. It captures the details of remodelling the IC testing problem as a search problem. To that effort, this chapter goes into the details of how a suitable state-space model is arrived and those fitness functions that can be used along with the search algorithms. In order to enable us to conduct some empirical studies to address key research questions, an experimentation framework is also developed. This chapter gives details of that experimental setup and how it will be used in the empirical studies which are to follow.

Chapter 4 - Suitability of Search-based Algorithms in IC Testing address the key question of whether search-based approaches are indeed suitable for applying in IC testing. It aims to conduct empirical studies to establish this suitability. It outlines the empirical study conducted on a 32-bit Arm platform with a simpler search-based algorithm, specifically simple hill-climbing algorithm. It drafts the research question to be addressed in this empirical study and describes the evaluation methodology to be followed while conducting this study. This chapter goes on to explain the results gathered from the study and provide conclusions based on the experiment's outcome.

Chapter 5 - Applying Advanced Search-based Algorithms in IC Testing details the evaluation of how some advanced search-based algorithms fare in handling the IC testing challenge. In this chapter we discuss the details of an empirical study conducted on a 64-bit Arm platform with advanced search-base algorithms like random-restart hill-climbing and simulated annealing and assess whether they provide any improvements over a local search algorithm like simple hill-climbing. The research question posed in this chapter focus on addressing the local maxima problem that can be impacting local search algorithms when applied to IC testing and it evaluates whether advanced algorithms can provide any benefits. It details the evaluation methodology followed in addressing the research questions and provide conclusions derived from the empirical study based on the observed results.

**Chapter 6 - Improving IC Testing with Multi-Objective Algorithms** looks at how to satisfy the real-world demands from IC testing when applying search-based approaches. Here we look beyond the mere suitability of search-based approaches and this chapter goes on to discuss the significance of multi-objective search algorithms in addressing the IC testing challenge. It goes on to detail the empirical study conducted on a 64-bit Arm platform with a multi-objective search algorithm called SPEA2. The research question posed in this chapter evaluate the suitability of multi-objective algorithms in satisfying the testing demands that are closer to the real-world testing needs for deeply embedded IC components. It aims to evaluate the benefits of using multi-objective algorithms over single objective algorithms in this IC testing problem. It also details the evaluation methodology followed in addressing the research question and provides a conclusion based on the results observed from the empirical study.

Finally the Chapter 7 - Conclusion and Future Work looks at the overall conclusions drawn from this research. It derives various conclusions based on the results obtained from the three empirical studies conducted as part of this research and aim to establish the benefits offered by the proposed search-based approach in IC testing. It looks at the relevance of this research beyond the current focus of IC testing from system level. Further looking into the future, this chapter describes the evolving landscape of IC testing and assess the continued relevance of this research with that future in mind. It also looks at further challenges that can be potential followups to this research.

#### 1.4 Contributory Publications

In this section it lists the various research publications done as part of engaging with the wider research community during the period of current research. Materials from these publications are used in various parts of this thesis - as all these publications came about as a direct result of the PhD research detailed in this thesis.

- Basil Eljuse and Neil Walkinshaw, "A Search Based Approach for Stress-Testing Integrated Circuits", At 8th International Symposium on Search-Based Software Engineering, SSBSE 2016, held in Raleigh, NC, USA, in October 2016. In: Sarro F., Deb K. (eds) Search Based Software Engineering. SSBSE 2016. Lecture Notes in Computer Science, vol 9962. Springer, Cham. (2016)

- Basil Eljuse and Neil Walkinshaw, "Comparison of Search Based Algorithms for Stress-Testing Integrated Circuits", At 10th International Symposium on Search-Based Software Engineering, SSBSE 2018, held in Montpellier, France, in September 2018. In: Colanzi T., McMinn P. (eds) Search-Based Software Engineering. SSBSE 2018. Lecture Notes in Computer Science, vol 11036. Springer, Cham. (2018)

- 3. Basil Eljuse and Neil Walkinshaw, "Application of Multi-Objective Search-Based Approach for Stress-Testing Integrated Circuits", STVR Journal - Submission accepted subject to amendments.

# Chapter 2 Background

In this chapter we look at the wider context of IC development to understand better the current development practices including those related to testing IC components. We also explain why testing CCI in particular is difficult from a system perspective and outlines how Search-Based Software Testing (SBST) becomes a natural avenue to explore while addressing this testing challenge.

First in Section 2.1 we look at testing in general as practiced within the industry and the typical challenges around testing which forms the wider context for the current research. As this research focus on the testing challenges around IC components, in Section 2.2 we look into the details of how IC development happens in the industry and how the current testing problem manifests in that development workflow. As part of gaining a more in-depth knowledge of CCI component (which is the focus of our research) we look at the details of CCI and how it is currently validated in Section 2.3 and the related testing challenges.

In Section 2.4 we describe why testing CCI from system level is a difficult problem and outline the key issue this research attempts to address. We explain how SBST forms a natural avenue to be investigated as part of this research in Section 2.5 and what options we have to address the problem at hand.

#### 2.1 Testing - A Perspective on Industry Practices

In this section we look at testing discipline in the way it is used within the industry so as to gain a broader understanding of what it pertains to and the key challenges in this domain. Many of the testing challenges addressed in this research do find relevance in the broader context of testing and hence this perspective will be helpful.

Testing is a key discipline employed in the industry as part of hardware and software engineering practices. Testing encompasses a wide variety of activities conducted during the development life-cycle, which often have varying goals defined based on the context in which it is applied. Bertolino [Ber07] explains the use of testing as part of quality assurance to validate the intended behaviour and identify potential malfunctions. That is a very board but general description of testing discipline. A more formal definition of testing process is described by Staats *et al.* [SWH11] and we will refer back to this formal definition when discussing testing aspects as seen from the industry. First let us inspect this formal definition.

The functional model of testing presented by Staats *et al.* [SWH11] defines a *testing system* as a collection of  $(P,S,T,O,corr,corr_t)$  where:

- S is a set of specifications

- *P* is a set of programs

- T is a set of tests

- O is a set of oracles

- $corr \subseteq P \times S$

- $corr_t \subseteq T \times P \times S$

Here the predicate *corr* is defined such that for  $p \in P$ ,  $s \in S$ , corr(p, s) implies p is correct w.r.t s. The predicate  $corr_t$  defines the correctness w.r.t a test  $t \in T$ , where  $corr_t$  holds good if and only if specification s holds for program p when running test t.

In the context of current testing of CCI component within an IC, the specification S corresponds to the Advanced Microcontroller Bus Architecture (AMBA)<sup> $\mathbb{B}$ </sup> Advanced eXtensible Interface (AXI)<sup>®</sup> protocol, which is used to implement the hardware cache coherency capability of the CCI (See Section 2.3.1 for additional details). The hardware implementation of the CCI logic would correspond to the program P. The data stall cycles events that can be monitored as part of the hardware logic block can be seen as the oracle O. The correctness *corr* can be one of the 2 aspects. One is the coherency of data managed by the CCI which would result in functional correctness. The second is the effectiveness with which this concurrency of data is ensured by CCI in a timely manner. From the perspective of stress testing of CCI component, the *corr* shows the correctness in terms of the effectiveness with which the implementation of S by P. As per the specification the occurrence of data stall cycles is a means to manage the stress on the component. Thus a test from Twould satisfy  $corr_t$  because that test would make the observation of the presence of data stall cycles which indicate the correctness of the implementation of S by P to indicate the CCI state when it is under stress.

Looking into the application of testing principles, there are multiple aspects of testing that presents us with very different challenges overall. Testing often starts with the definition of a 'test objective', which when defined in a given context drives the emphasis on testing and the process subsequently followed. The test objective for a project can be defined to achieve multiple goals like a) check if the right behaviour is observant from the product b) look for potential malfunctions c) check for conformance to standards d) assess release readiness e) gain user feedback and many more. For a given project it could be any one of the above or a combination of a few or even encompass all of the above mentioned aspects to be part of a test objective. This definition will eventually drive what type of activities gets done as part of testing. When looking this from a more formal definition, *test objective* always aims to check if a program P implements a specification S [SWH11]. Here the challenge had always been how formal the specification is for one to make use of it effectively in the testing process. But none-the-less specification S have a significant role in defining test T. In this research the focus is on non-functional testing rather than functional correctness which would have benefited from the specification being available.

Once the test objective is clear the industry practitioners plan for designing and developing different types of tests. During the test development these different types of tests are typically defined depending on the granularity of the UUT. The granularity of this testing target can be defined as unit testing, component testing, integration testing, system testing and system-of-systems testing. Some test type categorisations are based on the release milestones like Alpha testing, Beta testing, Product release testing etc. There are also different test types defined based on the system qualities (ISO 25010:2011 [ISOa] have a good framework for this) that are targeted by the tests such as functional testing, reliability testing, load testing, stress testing, security testing and usability testing. During the test development, the test practitioners apply different test techniques to identify test cases and two broad categories of test techniques are used in the industry: Black-box test techniques and White-box test techniques. Typically black-box techniques are specification based there is a test basis available to derive the test cases and the test practitioner sees the system as a black-box. These test basis (body of knowledge used as input for test analysis and design) could be requirements specification or design specifications that forms the input to the test designer other than software code itself. In case of white-box testing the test practitioner has software code as input and the structure based inputs from the code will drive the test design.

One of the key aspects involved in test design is related to 'test oracle' problem which is often signified by the extent to which observability O is accurate in representing the conformance of a program P in implementing its specification S. Barr *et al.* outline the various research efforts to address test oracle problem in their survey [Bar+15]. With the possibility of different types of tests being developed to achieve the very many objectives of the testing identified for a given project, the 'test selection and prioritisation' [Rot+99; Di +15] process becomes a key challenge for the industry practitioners. Yoo *et al.* detailed the challenge of test selection and prioritisation in the context of regression testing in their survey [YH10].

Another important challenge in the testing domain is determining when to stop testing or what amount of testing is enough. In terms of the formal definition the observability O and tests T signify the efficacy of the testing that is feasible. The 'test adequacy' refers to the aspect of testing which determines the stoppage criteria and is typically measured in the form of some coverage measurement. In some cases test adequacy criteria is defined as program-based, where the structural elements of the program in terms of control-flow and data-flow coverage [Hut+94] becomes the measures for test adequacy. There are other types of test adequacy measurements practiced - for example specification-based coverage criteria [HGW04; Raj06], where it looks at the coverage against a given specification. Moreover there are still further different approaches in defining test adequacy where it can be measured using a criteria that depicts it in terms of the fault-finding capabilities of the tests.

In our research we are focused primarily in the automated generation of tests with search-based approaches, thus focusing mostly on the challenges around test generation. While other test challenges might be relevant to the IC testing problem, we want to improve the test generation capability especially at system level.

We have looked so far at the general characteristics and challenges related to testing discipline in particular, which is deployed as part of wider hardware and software engineering development life-cycle. Let us look into more details on these engineering practices themselves where testing discipline gets employed. There are many different product development life-cycles which are adopted for hardware and software development in the industry. In case of hardware development, the engineering practices followed are very much of a phased manner - similar to waterfall, where the development progresses sequentially from one phase to another. This is a true reflection of the physical nature of the deliverable in case of hardware, where a strict ordering of activities is not only desirable but also is very essential. However in case of software there are many additional development life-cycles adopted in the industry beyond Waterfall - such as Agile, Iterative, V-Model, Rapid Application Development (RAD) and Spiral. When it comes to product development that includes both hardware and software, one of the prominent approaches adopted in industry is the hardware-software co-design development process. Some industry sectors like automotive which have to address stringent functional safety requirements (ISO 26262-1:2018 [ISOb]) follow an overlapped V-Model. So you can see that testing discipline is employed in a wide range of engineering process within the industry and most challenges related to testing are common and cut across these engineering practices.

As we have looked at a general overview of testing discipline in general and the various engineering processes that employs this discipline, let us look into some specific details of the IC development workflow in the next section.

# 2.2 IC Development: Understanding the Testing Context

First let us gather some detailed context on modern IC development process which was briefly mentioned in Chapter 1. We specifically seek to understand the engineering development life-cycle followed during IC development in order to understand not only the nature of development followed here, but also to better appreciate the inherent challenges in terms of testing, especially at the system level.

Hardware-Software co-design [Tei12] workflows allow the evolution of hardware and software development to happen in parallel. This is prevalent development model adopted by semiconductor Intellectual Property (IP) industry. There is a considerable overlap in the development timeline of these distinct components. This overlap in development time is a key factor which enables quicker time-to-market that fosters product innovations. Typically the hardware development will follow a more phased approach similar to waterfall, while software might be following Agile or other relevant software development life-cycles.

Hardware-software co-design is the de-facto industry practice in semiconductor industry sector and its popularity is underpinned by a range of factors that enables and equips the hardware and software to be developed in parallel. One of the main factors that enables this parallel development to happen is the availability of extensive tooling capabilities in this area. The evolution of Electronic Design Automation (EDA) [Rob15] facilitated the use of hardware-software co-design principles for IC development. The advancements in EDA tools massively improved multiple aspects of IC design like circuit and system design, timing analysis, synthesis, formal verification and many more.

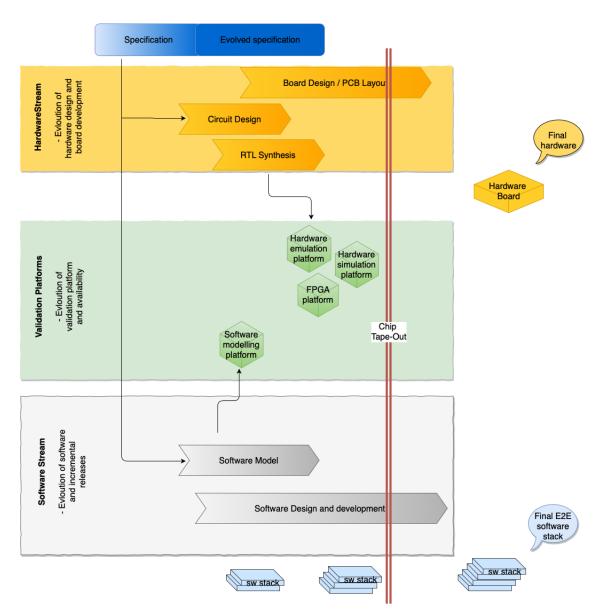

A typical scenario where a system design happens in a hardware-software codesign workflow is outlined in Figure 2.1. In the initial phase, the specifications for the system design happens. This would include the engineering specification which provides details of the various components of the overall system, its outline and layout. Based on this common specification both the hardware and software design and development streams would start evolving in parallel. The hardware development workflow progresses through synthesis, analysis and verification phases.

Figure 2.1: Hardware-Software Co-Design: A typical workflow

In parallel, the software development workflow progresses through the design, code development, integration and testing phases. These parallel streams converge at a point where the final hardware is available and the E2E software stack meant for that hardware is integrated as a complete system.

In the IC development workflow tape-out is a key intermediate milestone, where the IC is fabricated into a physical chip. Prior to the tape-out of the IC the output of the hardware workflows will undergo multiple stages of verification and validation. Here it uses EDA tools-based formal verification methodologies, hardware emulation and simulation platforms [Hua+11], Field Programmable Gate Array (FPGA) platform based testing [Hua+11] to perform the validation and verification of the IC. In case of the software stream the earliest platform available to perform validation are software models [CNR13] implementing the specification. As emulation and simulation platforms become available from the hardware stream, various software deliverables are also validated on these. These validation platforms have varying degree of accuracy in terms of representing the characteristics of the target hardware but none-the-less provides crucial early opportunities to validated the incremental versions of software's behaviour on the evolving hardware. Typically one would find software models, cycle-accurate software models, FPGAs, test-benches based on hardware emulators and power-aware hardware simulators as the early validation platforms made available for software validation. But none of these early testing truly enables a fully integrated system to be analysed for the final system behaviour. This remains a key goal yet to be fulfilled as the hardware and software development streams converge when the final hardware and the full E2E software stack is available. Real system behaviour is assessed on the final hardware with the E2E software stack.

Once the IC is taped-out then the system integration happens from a hardware perspective where typically the Printed Circuit Board (PCB) layout and board assembly is done. A number of board-level or platform-level tests are conducted and once ready software bring-up on the new system begins - starting with low-level firmware, progressively integrating the whole E2E software stack on that hardware board. More system level characterisation and bench-marking happens at this stage and final system gets released. This is the earliest opportunity we have for a full product to undergo system testing, where the final hardware and the full E2E software stack can be integrated and tested as a complete system. This also presents us with a key testing problem - only at this very late stage we have some capability to bring-up the full E2E software stack on the real hardware platform and test it from a full system context. This is the premise against which the current research is exploring for better testing approaches, in order to improve the current system testing practices in IC development. The specific aim being to be able to generate better automated stress tests with search-based approaches.

As detailed in this section we learnt about the typical workflow for IC development and the context in which our current research happens. Our aim is to define an improved test methodology to test some deeply embedded components developed as part of this above-mentioned workflow. As the performance of these components are critical in the final system behaviour it becomes important to do suitable system level tests to assess if there are any issues affecting final system performance. We look further into the details of current testing practices related to deeply embedded components in the subsequent section.

#### 2.3 CCI: Details and Testing Challenges

Now that we have understood the context in which IC development happens, let us try to learn more about CCI and what is all about. In this section we look into details of Arm CCI component, which is an essential part of modern Arm based chips, that is used to build a wide range of products including mobile phones, smart TVs, automotive infotainment and low cost infrastructure components. We also look at how testing gets done currently for CCI and the related testing challenges, which forms the key basis for this research's motivation.

#### 2.3.1 Understanding Cache Coherency and Role of CCI in IC Design

A cache memory is a high-speed memory component included in a Central Processing Unit (CPU) designed to speed up memory operations. With the evolution of multi-cluster, multi-core CPU architectures multi-level cache designs also became prevalent, where cache is arranged in multiple levels and CPUs have a requirement to access coherent data whenever they fetch memory contents from these cache.

First let us look a bit more into the history of the evolution of cache memory usage in IC design. CPU designs always exploited the performance benefits gained by the use of cache memory, especially when the gap between CPU speeds and memory access widened [JHS99] over time. With the advent of multi-core processor based system designs, the cache memory usage in these systems evolved to be based on hierarchical multi-level caches and various cache coherence protocols [AA17] got developed.

With the hierarchical multi-level cache, now we have systems with cache memory between CPU and main memory organised at multiple levels - with the faster (due to cost typically in smaller size) cache memory closer to CPU (called L1 cache) while comparatively slower but larger sized cache memories closer to the main memory (called L2 cache). Some modern systems have a further Level3 (L3) cache called as system level cache, which makes that particular multi-level cache configuration to have 3 levels. This indeed brought-in its own level of complexity in maintaining coherency at various levels [BW88] which also contributes to the resultant testability issues.

The above mentioned cache coherency management can be done either as a software or hardware solution. CCI is one such hardware solution which implements the cache coherency management entirely as hardware logic within an IC. Thus CCI can be explained simply as a hardware component that manages the coherent view of cache memory data for the users of cache in a system. CCI provides a basic interconnect functionality (connecting multiple components in the IC, similar to a system bus), but also provides cache coherency at hardware level as explained, which makes it a complex hardware logic unit.

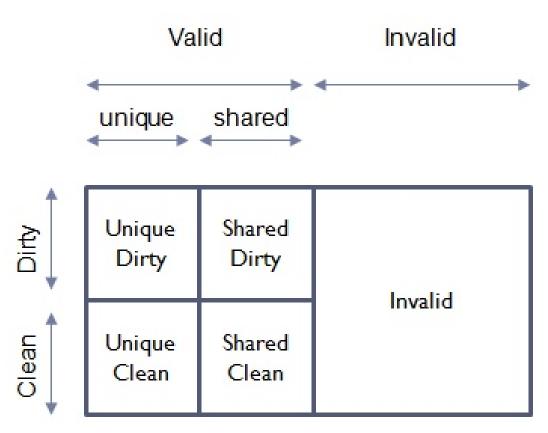

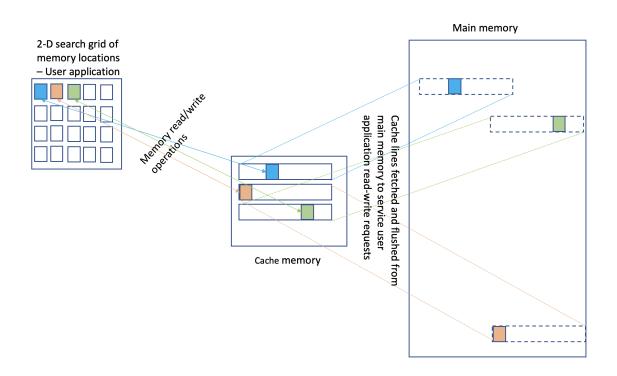

The diagram in Figure 2.2 outlines the coherency states as maintained by CCI during its operation. The hardware logic ensures the coherency of cache data, as seen by the users, based on the CCI state information. As part of providing this coherency at hardware level, CCI ensures that any data in the cache that is marked as 'shared' is always up-to-date and any consumer of that data can always see coherent data. At hardware level it tracks the cache validity and will flush and re-fetch cache data from memory (if found invalid) in order to ensure that the coherent view of data is maintained all the time.

Figure 2.2: CCI States - details

CCI performs this coherency management with the help of certain transactions (operations). CCI supports various transaction types as initiated by any user (called CCI 'master') to ensure the cache coherency. These transactions are defined and governed by a specification known as Arm AMBA® AXI® protocol. The following are the transaction groups:

• Non-shared - Read / Write

- Non-cached ReadOnce / WriteUnique / WriteLineUnique

- Cache Maintenance CleanShared / CleanInvalid / MakeInvalid

- Shareable Read ReadShared / ReadClean / ReadNotSharedDirty

- ShareableWrite MakeUnique / ReadUnique / CleanUnique and

- Write-Back WriteBack / WriteClean / Evict

In simple terms, CCI maintains the above mentioned state information. With the support of a series of transactions initiated by the various entities interacting with CCI, it performs the maintenance of cache coherency functionality. It is important to note that this is a complex functional block implemented in hardware and moreover this is a component which is deeply embedded that provides no direct interfaces to test it especially in a full system context.

#### 2.3.2 CCI in Real System Designs - TC2 and Juno

Knowing what is the basic purpose of CCI from Section 2.3.1, let us look at the details of a few real systems where CCI is used as part of an overall hardware design. In this research we specifically look at CCI400 [Arma] from the CCI product family. This has been used in real platforms with multi-core CPU clusters, all of which have access to a multi-level cache, managed by CCI.

Test Chip2 (TC2) [Armb] is a 32-bit Arm development board, which provides a reference implementation of Arm hardware design including CCI. This platform has multi-level cache accessed across 2 heterogeneous CPU clusters with different cache configurations. This variation in the Level2 (L2) cache size is as a result of the heterogeneous nature of CPU Clusters - due to difference in both CPU type and in CPU topology - which make the data access operations across clusters different in nature. The TC2 platform has a big cluster made of dual-core Cortex<sup>TM</sup>-A15 MPCore<sup>TM</sup>CPUs and a little cluster made of tri-core Cortex<sup>TM</sup>-A7 MPCore<sup>TM</sup>CPUs.

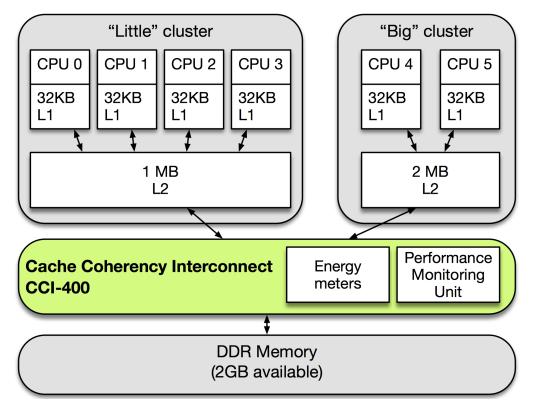

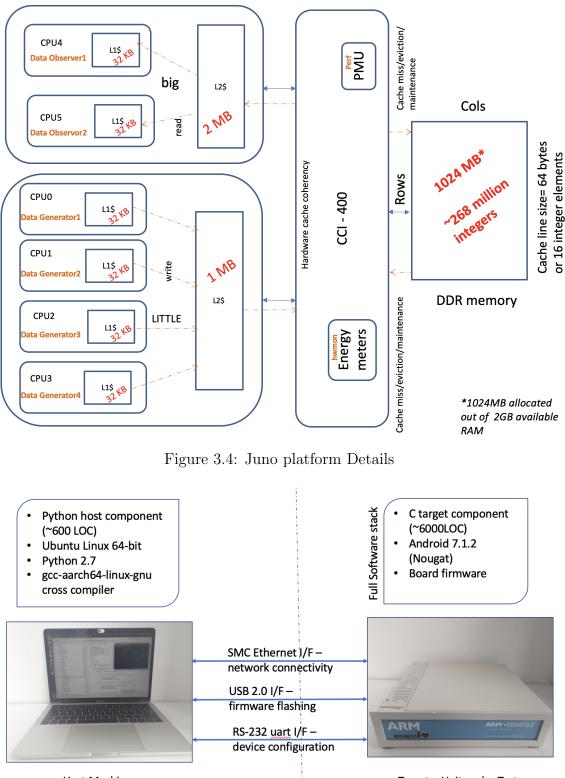

Juno [Armc] is a 64-bit Arm development board. Similar to the TC2 platform, Juno also has a heterogeneous cluster of CPUs with multi-level cache for data access and uses CCI400 for cache coherency management. However there are some significant differences between TC2 and Juno platforms, especially w.r.t cache configuration that needs to be noted.

There are multiple variants of Juno platform and in this study we chose the R0 variant of Juno platform. The Juno R0 platform has a big cluster made of dual-core Cortex<sup>TM</sup>-A57 MPCore<sup>TM</sup>CPUs and a little cluster made of quad-core Cortex<sup>TM</sup>-A53 MPCore<sup>TM</sup>CPUs. It has both Level1 (L1) and Level2 caches, with CCI-400

providing the interconnect and cache coherency across the 2 CPU clusters. Additionally Juno<sup>1</sup> also has a quad-core Arm Mali<sup>TM</sup>Graphics Processing Unit (GPU) with 128KB L2 cache.

Figure 2.3: Juno platform with CCI-400.

Figure 2.3 shows where the CCI sits in the context of a Juno platform design. Juno has two processor clusters, where different processors may require access to the same data (hence the need for a cache coherent interconnect). On Juno the little cluster has 1MB L2 cache compared to that of 512KB L2 cache in case of TC2 platform [Armb]. The big cluster on Juno platform has 2MB L2 cache compared to 1MB in case of TC2 platform [Armb].

The above described systems illustrate how CCI based systems can be used in systems with different configurations. One pertinent point from a testing perspective is that the CCI component sits below a mixture of complex hardware and software layers. We deploy a full Android software (released by Linaro [Lin]) stack and an user-space application that acts as test payload performing memory operations via CPU elements. Each memory operation is modulated by a L1 and a L2 cache. The CCI sits between the L2 caches for the various clusters and the physical memory. The CCI can in other words not be tested directly which compounds the testing challenge.

$<sup>^{1}</sup>$ All references of 'Juno' would imply R0 variant of the board in the rest of the thesis.

Some of the existing capabilities of CCI provides unique benefits in understanding the behaviour of this deeply embedded component during operation. These capabilities are highlighted in the below sections. They do have significant role in the the current research on improving stress testing of CCI from a full system context, hence let us look at them in detail.

**Performance Monitoring Unit: Capabilities** CCI includes a built-in component called the Performance Monitoring Unit (PMU) [Arma], which gathers various statistics about the operation of the interconnect at run-time and exposes them through counters monitoring certain events. Traditionally this had always been used for debug purposes. There are multiple counters and different event types that could be monitored using this PMU logic block. CCI-400 supports four 32-bit counters allowing one event per counter to be monitored in parallel. This means one can monitor up-to 4 events in parallel without incurring any penalty in performance.

One of the interesting events which are monitored by CCI is 'stall cycles' associated with various transactions. As a general rule of thumb, the occurrence of stall cycles indicates that the CCI component has to pause some of its operations to cope with the heightened demand for ensuring coherency. The count of these stall cycles can be used as a measure of stress in the system. Larger numbers of stall cycles can be an indication of stress in the platform leading to sub-optimal system performance. This increases the observability aspect of testability of this CCI component from system level, which should be considered beyond the traditional debugging context and should be exploited during testing.

**On-board energy meters: Capabilities** Juno has four on-board energy meters [Armc], which can be used to measure energy consumption during its operational state. These energy meters report various instantaneous measurements like voltage, current, power etc., across various sub-components of the system. This includes the energy measurements for the CCI component also.

CCI component's power measurement will be reported under the 'rest of the system components' in the System-on-Chip (SoC) group (a SoC is the IC that has all the various components such as CPU, GPU, various interconnects and input-output ports). This excludes power measurements for the CPU clusters and GPU within the SoC, which are normally measured and reported separately. These hardware monitor counters are exposed to the user via memory mapped registers, which can be read by a user application at set intervals. Energy measurement thus obtained provides an orthogonal but none-the-less important view of how optimally the underlying system is operating. Higher stress will manifest as larger energy consumption and hence could be used as an indicator of stress conditions related to this component.

#### 2.3.3 CCI: Current Testing Practices and Challenges

Now that we know the details of CCI and its functionality let us focus on the current set of verification methodologies employed during the testing of CCI. As in case of any other typical hardware IP component, the verification methodology for CCI do employ a range of standard techniques as below:

- 1. formal methods [Mar06].

- 2. constrained-random testing [Meh17].

- 3. protocol testing.

- 4. functional validation at various levels.

Hardware verification methodologies put great emphasis on Design for Testability (DfT) and provides a wide range of testability functions including that of builtin self-test functionality. In addition to the various tests targeting the hardware IP component in isolation, integration and system tests are also performed, some with specialised software stack mimicking typical complex software behaviours with synthetic test payloads.

With the software development progressing alongside the development of hardware components, the initial testing at a system level is often limited to early software bring-up activities which have a limited scope in terms of testing. Here the various software components which are part of the full E2E stack are brought up on the hardware platform. The early bring-up stage mainly focuses on enabling enough minimal software to be brought up. This allows the hardware to be extensively tested for stability and other characteristics which are critical part of this early bring-up stage. These platform characterisations will include understanding the thermal limits, power envelop, leakage currents, operating voltage and frequencies etc, all of which could lead to hardware level adjustments before the full system software tests could be commenced. It is important to note that this early bring-up stage does not provide the opportunity for a full-fledged system testing to assess the system behaviour with the E2E software stack. This is because here we are still stabilising the hardware and ensuring safe operational limits are determined and then set before any full system testing can happen.

Looking at the existing testing practices, predominantly cache memory testing had been focused on functional correctness, especially at an individual component level. Being a hardware component, most of these functional tests are based on hardware self-tests [The+13] [The+14]. Given that cache behaviour is critical to the overall system performance, there is an increasing need to focus on non-functional testing of this deeply embedded component at a system level. There have been some recent efforts to auto-generate stress tests for cache coherency at SoC level by You *et al.* [You+16]. Here the target of testing is SoC (at hardware level), which is the IC that has all the various components like CPU, various interconnects and inputoutput ports. This employs generation of random test vectors with synthetic traffic generators at a SoC level. This provides advantages in terms of having additional coverage when compared to traditional cache testing. However this approach still does not provide the ability to test cache behaviour from a full system context with E2E software stack; instead it is done at the SoC level.

**System Testing Limitations** When CCI moves to system level testing, we are able to exercise the full E2E stack on the real hardware. However CCI being deeply embedded it is now under multiple layers of hardware and software components with no direct interfaces to interact with. This makes CCI testing at system level very difficult. None-the-less CCI is still considered a critical component of the IC design whose performance can impact the overall system behaviour. There is a much higher emphasis on non-functional testing like stress testing to be conducted on this CCI component in a full system context. The CCI component has many tunable configurations that can be set when integrated into the full system. It is not possible to exhaustively test these configurations at component level. Moreover the CCI component behaviour can be affected by other components integrated within the system. All these factors makes it important that we perform effective testing of CCI in a full system context.

Currently, tests are largely developed by hand for system testing of cache behaviour. In order to cater for specific configurations - based on specialist knowledge of the target system - separate tests are designed. The downside of this is that there is very limited reuse of such tests; a slight change in configurations can lead to very different behaviours, necessitating very different test sets. Automating an approach to generate these tests would improve the re-usability and an overall reduction in the time and effort required to test these complex IC based systems.

As one can see from the above description, testing CCI which manages cache coherency of a multi-level cache based system is difficult. This difficulty is further increased when we want to perform these tests from a full system context which is a very important goal before the final product release. This research aim to address this specific testing challenge in the context of testing CCI from system level.

#### 2.4 Problem Statement

With the detailed understanding of CCI and deeply embedded components in general, especially looking at the testing challenges in this area, let us try to understand why CCI testing is difficult and describe the problem this current research is addressing.

The problem statement for this research can be summarised as:

Deeply embedded components such as CCI are critical to the performance of IC based systems. Current testing practices have limited capabilities in effectively stress testing this critical component from the system level. The lack of direct interfaces to this deeply embedded component poses a number of testability challenges which cannot be addressed by traditional test methods. This research aim to devise a test methodology which can effectively stress test the CCI component from system level as a means to expose any performance issues that can affect the final system behaviour. Thus it aims to improve the overall system level testing capabilities of IC testing, specifically targeting deeply embedded components like CCI.

One of the fundamental research questions we want to address is whether searchbased test methodology could be suitable for addressing the testing challenge posed by deeply embedded IC components. This is reflected in the first research question we address where we evaluate the suitability of search-based algorithms in generating stress tests for deeply embedded IC components.

Let us now inspect why CCI is particularly hard to test from a system level. From a testing perspective the multi-level cache (See Section 2.3.1) in IC designs introduce run-time behaviours which are hard to control, because the cache state at each level is inter-dependent and the cache operations at one level would impact the state of cache memory at a different level in the hierarchy. This results in the difficulty to determine the cache states at run-time, which in turn makes the validation of multi-level cache very challenging. This is more challenging in case of system testing where these run-time interactions and state changes are even harder to control or to determine.

Let us look into the details of what are the multiple factors that contribute to testability [VM95] such as 'Observability' and 'Information Loss' in addition to the traditional definition of testability, which states testability as the ability to set a test criteria and perform tests in order to determine if a given test criteria is met or not. In simple terms 'testability' can be stated as:

- how easy it is to see the internal operations during a test to determine if a test criterion is met. This maps with 'Observability' aspect of testability.

- whether all the internal state change information is visible via the final output. This maps with 'Information Loss' aspect of testability.

- how easy it is to generate a test criterion in order to perform an operation and assert if that test criterion is indeed met or not.

With the understanding of what typically testability means now let us look at testability in relation to the CCI component. Let us analyse the testing challenges w.r.t CCI component in a full system context which includes testability and others challenges. These are outlined below:

- CCI is at the bottom of a complex software and hardware stack. During operation it is difficult to provide direct inputs to the CCI component as part of setting a test criteria and performing a test to evaluate if that criteria is being met. This makes it poorly testable from system level.

- CCI is implemented alongside complex functionality like multi-stage pipelines and speculative fetch all of which introduce run-time behaviours that are hard to control. This adds to the difficulty in setting a test criteria and performing a test to evaluate that criteria, which again results in the poor testability of the component.

- CCI deals with multi-level cache hierarchies which makes it difficult to observe the detailed internal states during its operation. This makes the 'Observability' criteria for CCI component quite low.

- Cache maintenance operations happening within CCI at various levels will not be readily understood by looking at the final state of the basic memory readwrite operations. This results in the 'Information Loss' criteria for CCI to be considered as high making it a poorly testable component.

- CCI being a highly reconfigurable component at both design and run-time makes it expensive to test all configurations.

Looking at the testability challenges associated with the CCI component we want to analyse whether complex search-based algorithms can better address the testing challenges posed by IC testing. In the second research question we specifically evaluate how better complex search-based algorithms might be able to generate stress tests targeting IC components.

Considering the critical nature of CCI in the final system behaviour and the above listed testability challenges, it would be beneficial to come up with an effective test methodology to stress test this component in full system context. If this test methodology can generate the tests in an automated manner then this can address the issue related to the lack of reusability of tests also, which is another factor that affects the current test practices. When focused on testing deeply embedded IC components, it is critical to ensure that search-based approach can handle multiple stress factors. In this research as part of the third research question, we evaluate whether multi-objective search algorithms can generate better stress tests targeting deeply embedded IC components.

Now that we have understood the key problem addressed in this research, let us look at the potential of exploiting search-based approaches in solving this problem. The next section gives an outline of what options search-based approaches presents to us in addressing this testing challenge and how it provides the motivation for this research.

#### 2.5 Search-Based Software Testing (SBST)

In the earlier sections we looked at the wider background of IC development and the testability issues affecting deeply embedded components like CCI. With a clear understanding of the problem at hand let us look at the search-based approaches and see how it can help in addressing the testing challenges posed by CCI. Let us look more into the various offerings from SBST methodology. First we look at related research on cache testing in general and the current application of SBST in the context of cache testing. Subsequently we look at various options offered by SBST approaches which is seen as a natural avenue to explore to solve the complex testing challenge related to CCI.

#### 2.5.1 Related Research

The focus of this research is on the application of SBST methods for system testing in the context of testing deeply embedded hardware components from system level. Application of search-based test techniques are not new at system level testing and in particular targeting non-functional system properties including performance analysis as explained by Shen *et al.* [She+15]. This uses genetic algorithms relying on a combination of search-based heuristics and utilises data mining of execution traces to identify performance bottlenecks.

Further surveys by Afzal *et al.* [ATF09] confirms its application being extended to other non-functional system attributes such as safety [BPS03], usability, quality of service [Can+05] and security [Del+05]. From these it is clear that search-based algorithms can be applied to testing a range of non-functional system properties. This survey shows the use of a range of search-based algorithms including simpler ones such as hill-climbing, Simulated Annealing and population based algorithms like Genetic algorithms, Ant colony, particle swarm optimisation etc. So it does provide us with a wide range of options which is encouraging.

SBST has often been used in the context of software testing and much less for hardware testing. Most of the search-based software testing techniques applied on hardware uses Hardware-In-the-Loop (HIL) systems [WK09; LW10]. Wegener *et al.* developed a framework that integrates an evolutionary testing framework with a testing platform that supports model-in-the-loop [Mut+11], software-in-the-loop [CS16] and HIL testing of embedded systems in an industrial usage context where it describes the testing of an antilock-braking system electronic control unit. Lindar *et al.* present an approach in which evolutionary functional testing is performed using an actual electronic control unit for test case evaluation with HIL systems. One notable advantage of HIL systems is that they provide additional testability components and interfaces which supports the application of search-based algorithms, which may not be the case for other hardware system testing scenarios. In the current study we are applying search-based algorithms on hardware components without the typical HIL setup, but seeking to employ alternate methods to test deeply embedded IC components at system level.

In relation to the testing of CCI components at system level we want to analyse the existing state-of-the-art techniques in terms of cache testing especially focusing on the non-functional testing of cache component at system level. At a broader level, we can see that search-based algorithms are successfully used in stress testing of real-time systems [BLS05]. Briand *et al.* implemented the application of searchbased algorithms in a tool that could actually help testers identify test cases that will likely stress the system to such an extent that some tasks may miss deadlines. Alesio *et al.* [Ale+15] show how search approaches can be successfully used in stress testing.

In this research we aim to focus on the testing of CCI component which performs cache coherency management in the system. Typically most of the testing around cache memory and cache coherency are functional tests in nature [QM12]. Qin et al. developed an efficient test generation technique, which can be used to achieve full state and transition coverage in simulation based verification for a wide variety of cache coherence protocols. But this is mainly focused on testing functional correctness and what we need for our research problem is to focus on non-functional testing. All the prevalent research into cache testing are mostly focused on hardware self-tests [The+13; The+14]. Theodorou et al. developed a SBST program development methodology used for on-line testing of small cache memories in microprocessors. We also found that some recent research do investigate the possibility of auto-generation of stress tests targeting cache coherency at SoC level [You+16]. But crucially this was still targeted at SoC level rather than system level. You *et al.* developed a SoC system level cache coherence stress tester called 'Red Baron', which automatically generates test cases on the fly, taking into account the behavior of the CPU's cache, Input-Output (IO) coherence, system memory and interconnect. Successful application of SBST methodology in the area of memory system validation can be seen in the work using genetic algorithms with Memory Consistency Model (MCM) verification as per [EN16]. Elver *et al.* developed a test generation framework called 'McVerSi', which employs a Genetic Programming (GP) based approach to MCM test generation. 'McVerSi' relies on a novel crossover function that prioritizes memory operations contributing to non-determinism, thereby increasing the probability of uncovering MCM bugs. Further we could see that in the area of testing cache coherency management, again the focus had been mostly on functional testing as explained in [Acl+15]. Acle *et al.* proposes a method to test the cache coherence logic existing within each core in a multi-core system with ability to detect hardware defects affecting this logic. All these related research encourage us to explore SBST domain to address the CCI testing challenge we attempt to solve with this research.

We can see that there is a good amount of research on the use of search-based algorithms for improving system level testing and in the cache memory testing domain. This puts us in a firm footing and gives us the confidence to explore the use of search-based algorithms in addressing the testability challenges posed by CCI component in a system context.

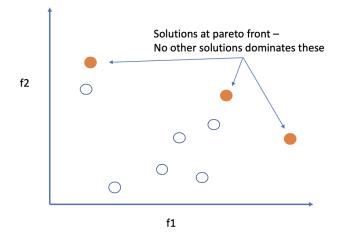

#### 2.5.2 SBST: Solution Options

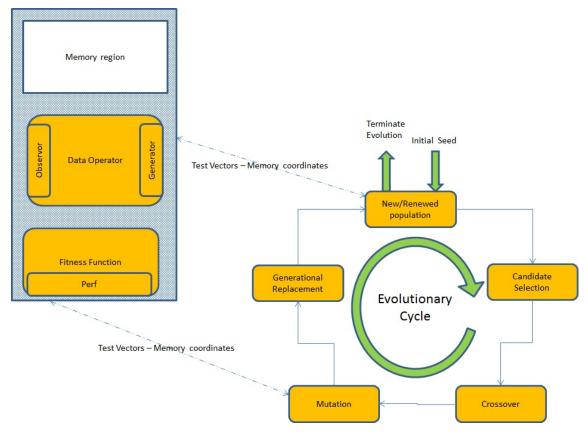

SBST techniques re-frame the testing challenge as a search-problem [McM04]. This can support test automation by leaving the selection and execution of test cases to an algorithm, which selects test inputs with the aim of optimising some objective. This approach is particularly suitable in cases where a) the search-space is large [Ber07] and b) there is higher levels of non-determinism during the test execution [BLS05], which drives the popularity of SBST for automated test generation [Har07]. By defining a suitable fitness function and allowing the algorithm to explore the searchspace, it presents us with a very optimal approach to tackle such complex testing scenarios akin to the CCI testing problem outlined in the previous section.